Description

The DS26LS32 and DS26LS32A are quad differential line receivers designed to meet the RS-422 RS-423 and Federal Standards 1020 and 1030 for balanced and unbalanced digital data transmission The DS26LS32 and DS26LS32A have an input sensitivity of 200 mV over the input voltage range of g 7V and the DS26LS33 and DS26LS33A have an input sensitivity of 500 mV over the input voltage range of g 15V Both the DS26LS32A and DS26LS33A differ in function from the popular DS26LS32 and DS26LS33 in that input p

Features

- TRI-STATE outputs with 8 mA sink capability Constructed using low power Schottky processing these devices are available over the full military and commerical operating temperature ranges

Features

Y

Y

Y

Y

Y Y

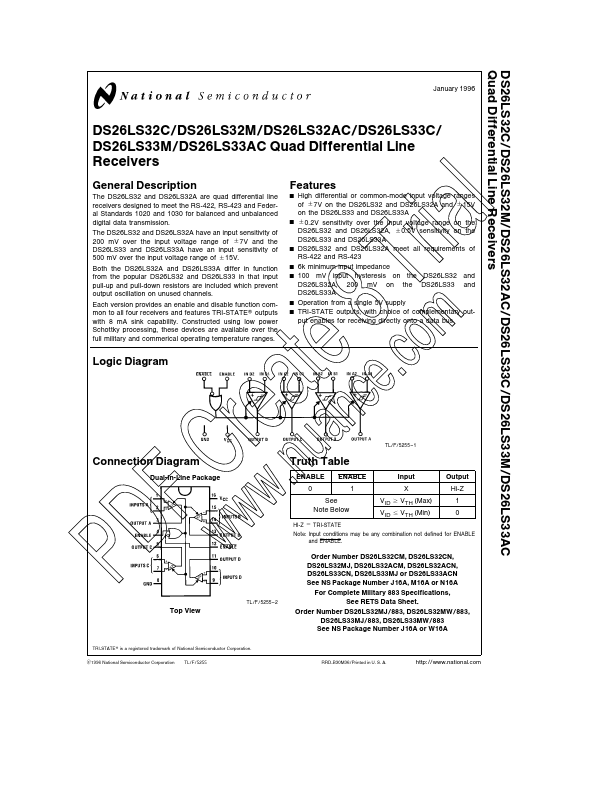

Logic Diagram

r e . n a

ww

0

TL F 5255.

- 2

TL F 5255

ua

ENABLE

HI-Z e TRI-STATE

t e n

Truth Table

1 See Note Below

Connection Diagram

F w C

Dual-In-Line Package Top View

ce. TL F 5255.

- 1

8 c T

ENABLE Input X

RRD-B30M36 Printed in U S A

Y

om

VID t VTH (Max) VID s V.