Description

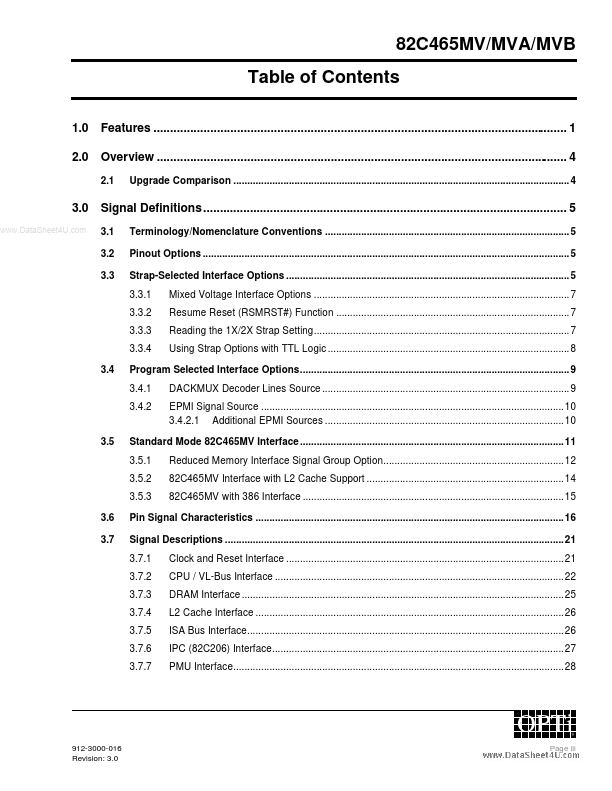

21 3.7.1 3.7.2 3.7.3 3.7.4 3.7.5 3.7.6 3.7.7 Clock and Reset Interface 21 CPU / VL-Bus Interface 22 DRAM Interface 25 L2 Cache Interface 26 ISA Bus Interface26 IPC (82C206) Interface27 PMU Interface28

OPTi

912-3000-016 Revision: 3.0

®

Page iii

82C465MV/MVA/MVB

Table of Contents (cont.)

3.7.8 3.7.9 Miscellaneous Signal Interface 30 Power and Ground Pins 31

4.0

Functional Description 33

4.1 4.2 463/465 Chipset Programming Comparison 33 CPU and VL-Bus Interface 33 4.2.1 4.2.2 Basic Command

Features

- 1 Overview 4

2.1 Upgrade Comparison 4

3.0

www. DataSheet4U. com

Signal Definitions 5

3.1 3.2 3.3 Terminology/Nomenclature Conventions 5 Pinout Options 5 Strap-Selected Interface Options 5 3.3.1 3.3.2 3.3.3 3.3.4 3.4 Mixed Voltage Interface Options 7 Resume Reset (RSMRST#) Function 7 Reading the 1X/2X Strap Setting 7 Using Strap Options with TTL Logic 8

Program Selected Interface Options 9 3.4.1 3.4.2.