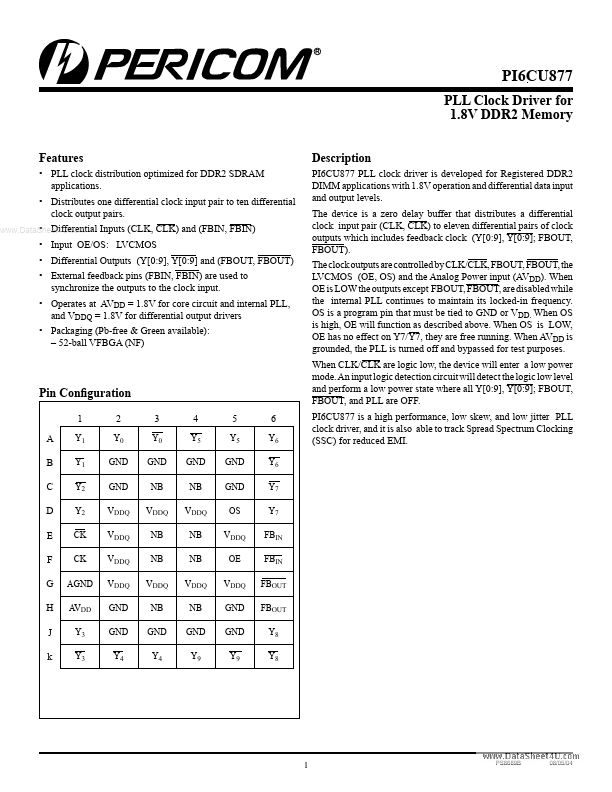

PI6CU877 Overview

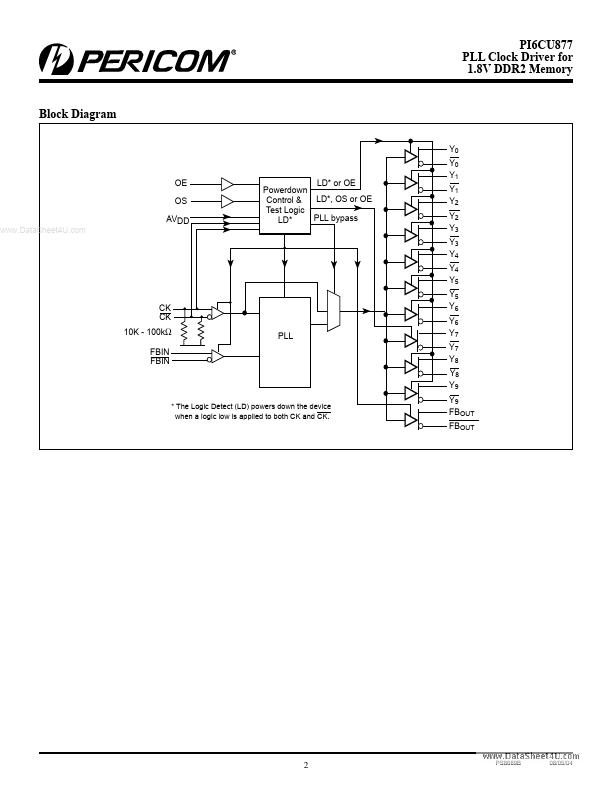

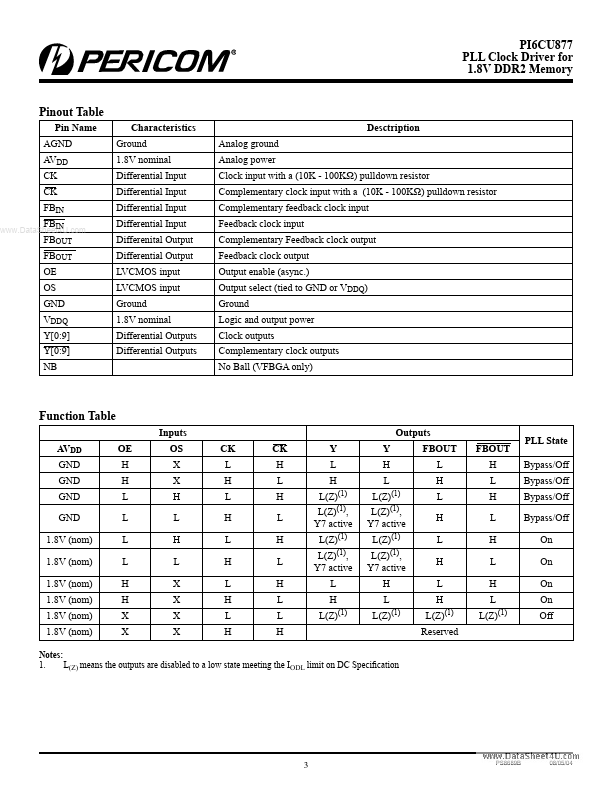

PI6CU877 PLL clock driver is developed for Registered DDR2 DIMM applications with 1.8V operation and differential data input and output levels. The device is a zero delay buffer that distributes a differential clock input pair (CLK, CLK) to eleven differential pairs of clock outputs which includes feedback clock (Y[0:9], Y[0:9]; The clock outputs are controlled by CLK/CLK, FBOUT, FBOUT, the LVCMOS (OE, OS) and the...

PI6CU877 Key Features

- PLL clock distribution optimized for DDR2 SDRAM

PI6CU877 Applications

- Distributes one differential clock input pair to ten differential clock output pairs