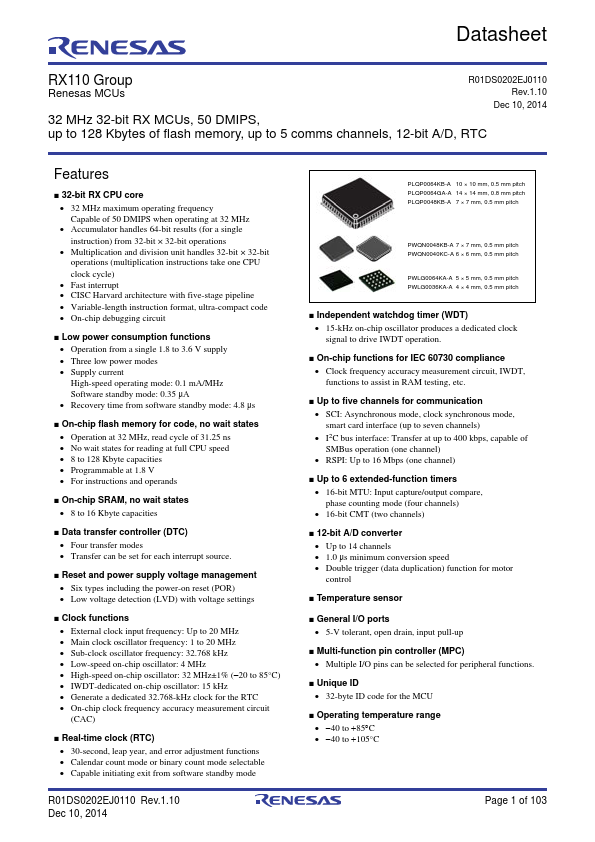

R5F51104ADLF

Description

CPU CPU Maximum operating frequenc.

Key Features

- On-chip SRAM, no wait states 8 to 16 Kbyte capacities

- Data transfer controller (DTC) Four transfer modes Transfer can be set for each interrupt source

- Reset and power supply voltage management Six types including the power-on reset (POR) Low voltage detection (LVD) with voltage settings

- Independent watchdog timer (WDT) 15-kHz on-chip oscillator produces a dedicated clock signal to drive IWDT operation

- On-chip functions for IEC 60730 pliance Clock frequency accuracy measurement circuit, IWDT, functions to assist in RAM testing, etc

- 12-bit A/D converter Up to 14 channels 1.0 μs minimum conversion speed Double trigger (data duplication) function for motor control

- Temperature sensor

- General I/O ports 5-V tolerant, open drain, input pull-up

- Multi-function pin controller (MPC) Multiple I/O pins can be selected for peripheral functions

- Unique ID 32-byte ID code for the MCU