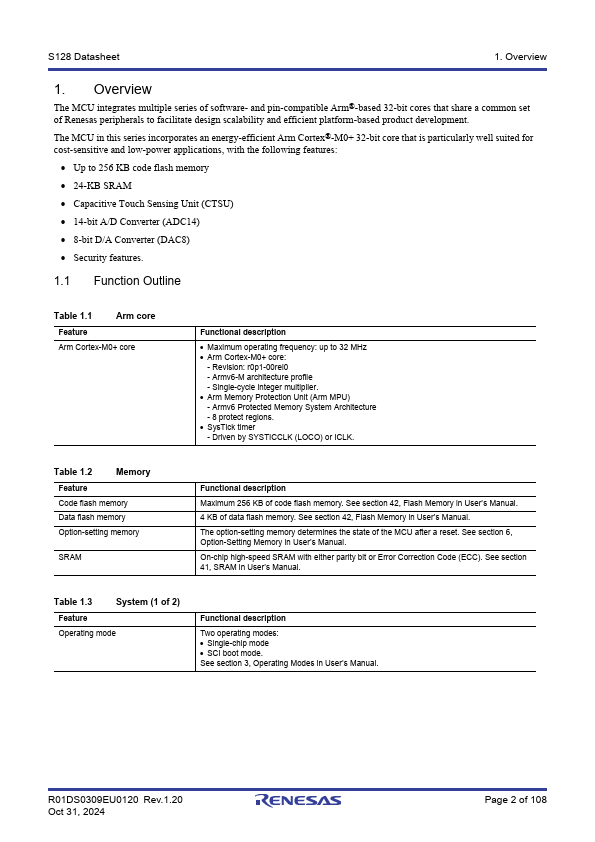

Description

Maximum operating frequency: up to 32 MHz

Arm Cortex-M0+ core:

- Revision: r0p1-00rel0 - Armv6-M architecture profile - Single-cycle integer multiplier.

Arm Memory Protection Unit (Arm MPU) - Armv6 Protected Memory System Architecture - 8 protect regions.

SysTick timer - Driven by SYSTICCLK (LOCO) or ICLK.

Features

- Features.

- Arm Cortex-M0+ Core.

- Arm®v6-M architecture.

- Maximum operating frequency: 32 MHz.

- Arm® Memory Protection Unit (Arm MPU) with 8 regions.

- Debug and Trace: DWT, BPU, CoreSight™ MTB-M0+.

- CoreSight Debug Port: SW-DP.

- Memory.

- Up to 256-KB code flash memory.

- 4-KB data flash memory (100,000 erase/write cycles).

- Up to 24-KB SRAM.

- Memory protection units.

- 128-bit unique ID.

- Connectivity.

- USB 2.0 Full-Speed (USBFS) module - On.