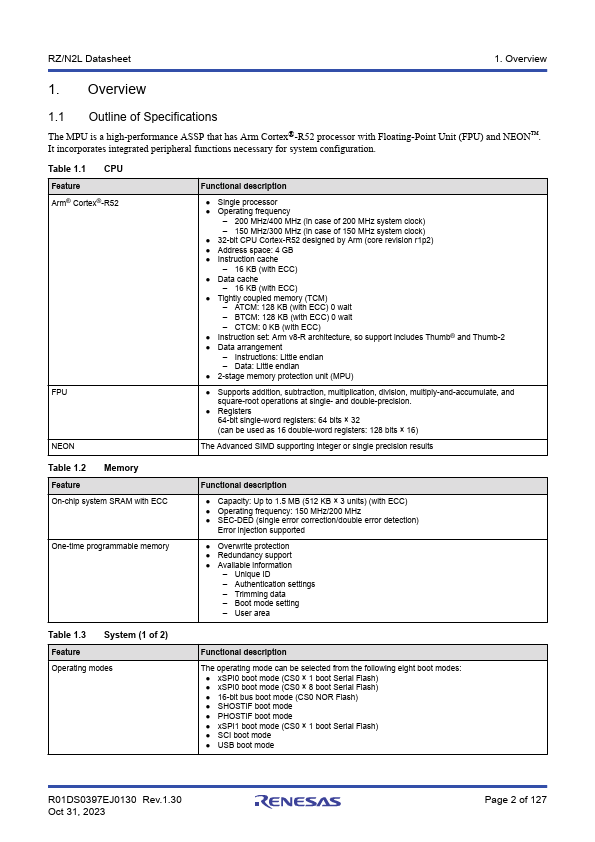

Description

Single processor

Operating frequency

200 MHz/400 MHz (in case of 200 MHz system clock)

150 MHz/300 MHz (in case of 150 MHz system clock)

32-bit CPU Cortex-R52 designed by Arm (core revision r1p2)

Address space: 4 GB

Instruction cache

16 KB (with ECC)

Data cache

16 KB (with ECC)

Tightly coupled memory (TCM)

ATCM: 128 KB (with ECC) 0 wait

BTCM: 128 KB (with ECC) 0 wait

CTCM: 0 KB (with E

Features

- On-chip 32-bit Arm Cortex-R52 processor.

- High-speed realtime control with operating frequency of 200/400 MHz.

- On-chip Single 32-bit Arm Cortex-R52 (revision r1p2).

- Tightly coupled memory (TCM) with ECC.

- CPU0: 128 KB/128 KB.

- Instruction cache/data cache with ECC.

- CPU0: 16 KB per cache.

- High-speed interrupt.

- The FPU supports addition, subtraction, multiplication, division, multiply-and-accumulate, and square-root operations at singleprecision.