Description

Frequency margining

Digital PLLs

CPU / FPGA FIFO control

Adaptive synchronization

Agile RF local oscillators

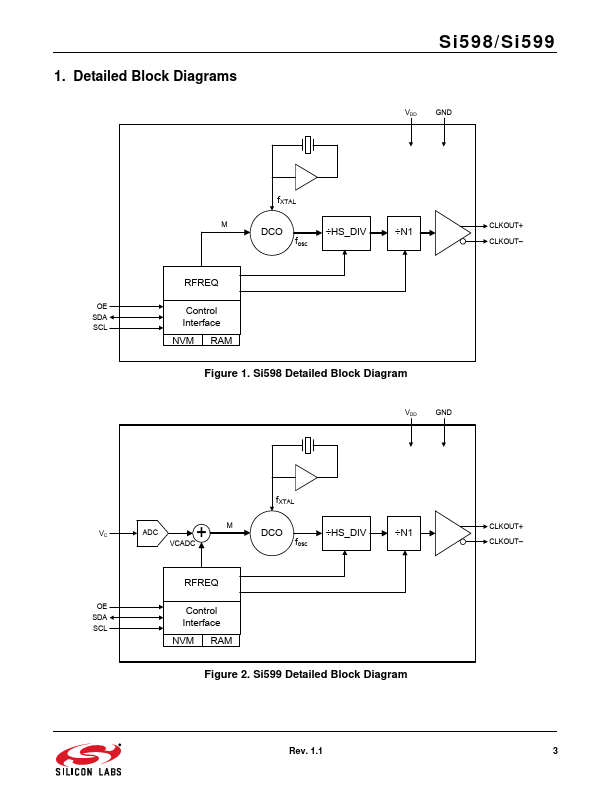

The Si598 XO/Si599 VCXO utilizes Silicon Laboratories' advanced DSPLL® circuitry to provide a low-jitter clock

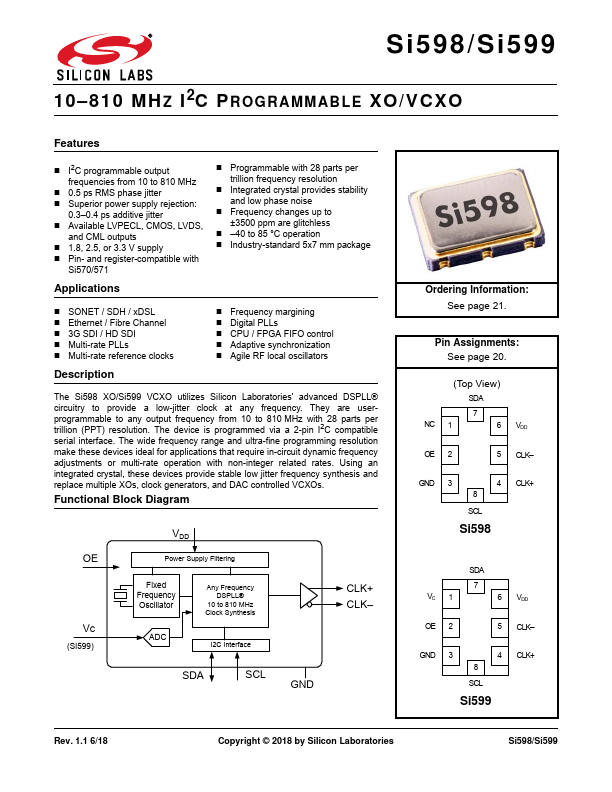

Features

- I2C programmable output frequencies from 10 to 810 MHz.

- 0.5 ps RMS phase jitter.

- Superior power supply rejection:

0.3.

- 0.4 ps additive jitter.

- Available LVPECL, CMOS, LVDS,

and CML outputs.

- 1.8, 2.5, or 3.3 V supply.

- Pin- and register-compatible with

Si570/571.

- Programmable with 28 parts per trillion frequency resolution.

- Integrated crystal provides stability and low phase noise.

- Frequency changes up to ±3500 ppm are glitchless.