SEU02G64B4BF2SA-25R

Features

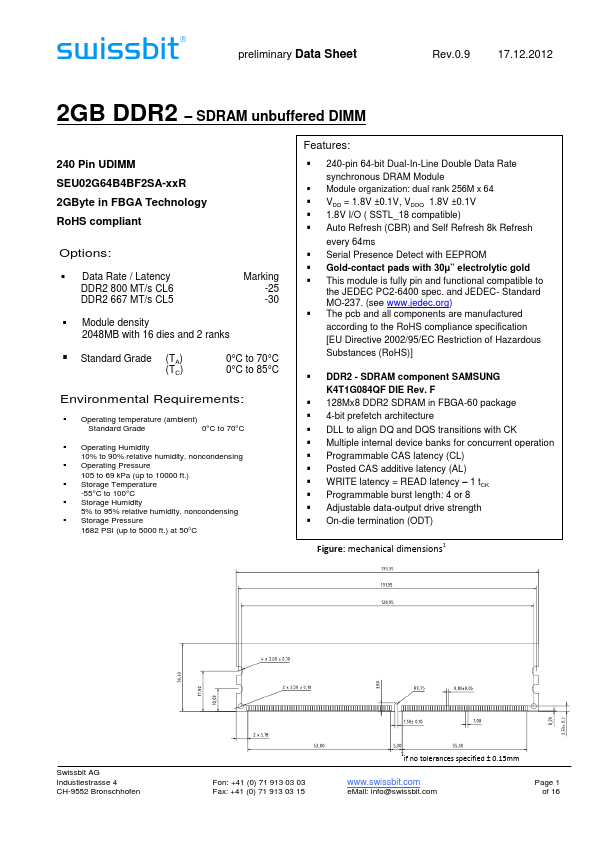

: 240 Pin UDIMM SEU02G64B4BF2SA-xx R 2GByte in FBGA Technology Ro HS pliant

Options:

- Data Rate / Latency DDR2 800 MT/s CL6 DDR2 667 MT/s CL5 Module density 2048MB with 16 dies and 2 ranks Standard Grade (TA) (TC) 0°C to 70°C 0°C to 85°C Marking -25 -30

- -

240-pin 64-bit Dual-In-Line Double Data Rate synchronous DRAM Module

Module organization: dual rank 256M x 64

- -

- -

- -

- -

- VDD = 1.8V ±0.1V, VDDQ 1.8V ±0.1V 1.8V I/O ( SSTL_18 patible) Auto Refresh (CBR) and Self Refresh 8k Refresh every 64ms Serial Presence Detect with EEPROM Gold-contact pads with 30µ” electrolytic gold This module is fully pin and functional patible to the JEDEC PC2-6400 spec. and JEDEC- Standard MO-237. (see .jedec.org) The pcb and all ponents are manufactured according to the Ro HS pliance specification [EU Directive 2002/95/EC Restriction of Hazardous Substances (Ro HS)] DDR2

- SDRAM ponent SAMSUNG K4T1G084QF DIE Rev. F 128Mx8 DDR2 SDRAM in FBGA-60 package 4-bit prefetch architecture DLL to...