Description

56

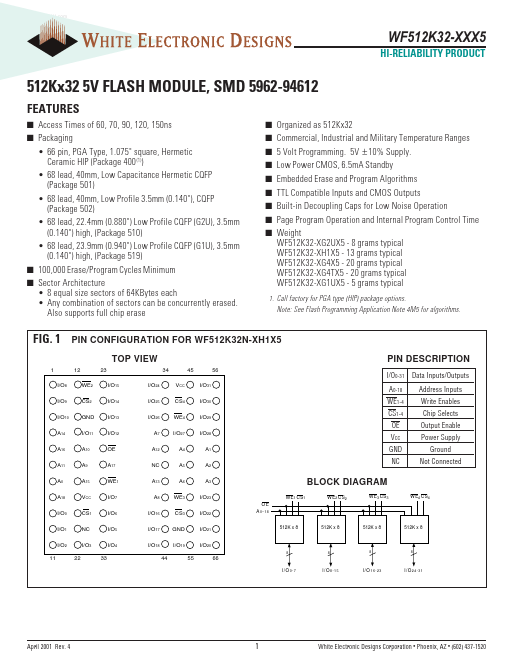

I/O0-31 A0-18 WE1-4 CS1-4 OE VCC GND NC

Data Inputs/Outputs Address Inputs Write Enables Chip Selects Output Enable Power Supply Ground Not Connected

BLOCK DIAGRAM

W E1 CS1 OE A0-18 512K x 8 512K x 8 W E2 CS2 W E3 CS3 W E4 CS4

512K x 8

512K x 8

66

I/O0-7 I/O8-15 I/O16-23 I/O24-31

April 2001 Rev.4

1

White Electronic Designs Corporation

Phoenix, AZ

(602) 437-1520

WF512K32-XXX5

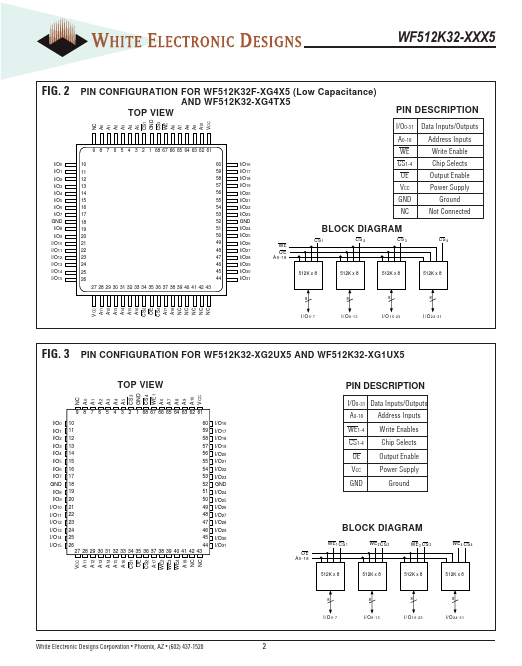

FIG.2

PIN CONFIGURATION FOR WF512K32F-XG4X5 (Low Capacitance) AND WF512K32-XG4TX5 TOP

Features

- s Access Times of 60, 70, 90, 120, 150ns s Packaging.

- 66 pin, PGA Type, 1.075" square, Hermetic Ceramic HIP (Package 400 (1)).

- 68 lead, 40mm, Low Capacitance Hermetic CQFP (Package 501).

- 68 lead, 40mm, Low Profile 3.5mm (0.140"), CQFP (Package 502).

- 68 lead, 22.4mm (0.880") Low Profile CQFP (G2U), 3.5mm (0.140") high, (Package 510).

- 68 lead, 23.9mm (0.940") Low Profile CQFP (G1U), 3.5mm (0.140") high, (Package 519) s 100,000 Erase/Program Cycles Minim.