TPT9L484

Features

- Exceeds the LVDS Standard TIA/EIA-644 for High speed Data Interchange

- Low-Voltage Differential 100-Ω (typical) Line Receivers for Signaling Rates, Up to 400 Mbps, 200Mbps Clock

- 3.3-V Power Supply Design

- 6 ns Maximum Propagation Delay

- 0.1 ns Differential Skew (Typical)

- Accepts Small Swing (350 m V Typical) VID

Supports Open, Short, and Terminated Input Fail-Safe

- Power Down High Impedance on LVDS Inputs

- Bus-Pin Protection: ±8 k V HBM model

- - 40°C to 85°C Operation Temperature Range

Multipoint-LVDS Line Driver and Receiver

Description

The TPT9L484 is a 3.3V 4-CH Low-Voltage Differential (LVDS) line receivers, which can support 400 Mbps data rates. Receiver inputs are protected against ±8k V ESD strikes without latch-up.

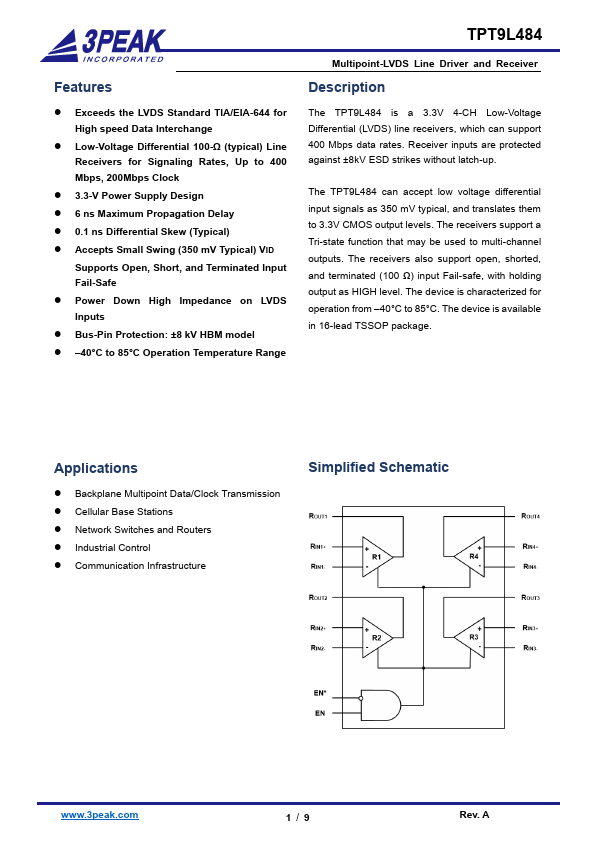

The TPT9L484 can accept low voltage differential input signals as 350 m V typical, and translates them to 3.3V CMOS output levels. The receivers support a Tri-state function that may be used to multi-channel outputs. The receivers also support open,...