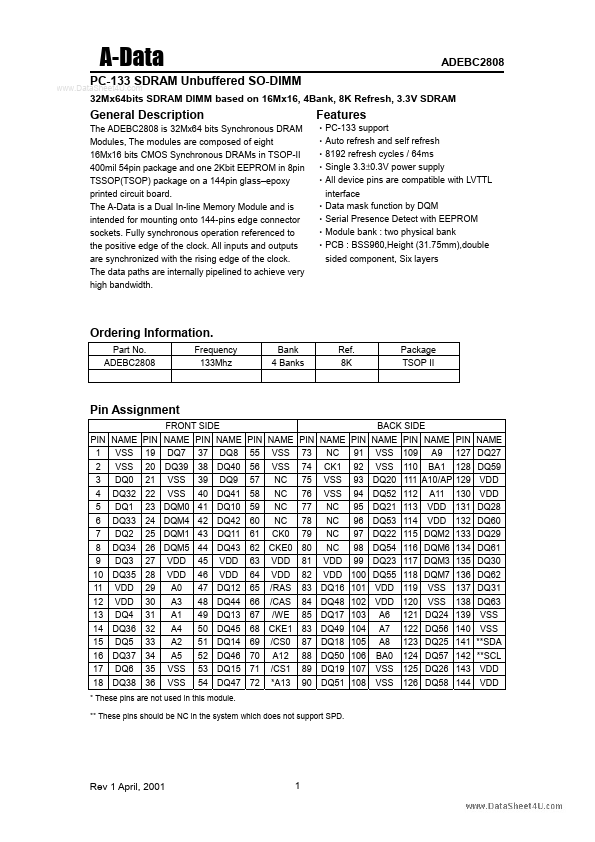

ADEBC2808 Overview

Description

The ADEBC2808 is 32Mx64 bits Synchronous DRAM Modules, The modules are composed of eight 16Mx16 bits CMOS Synchronous DRAMs in TSOP-II 400mil 54pin package and one 2Kbit EEPROM in 8pin TSSOP(TSOP) package on a 144pin glass–epoxy printed circuit board. The A-Data is a Dual In-line Memory Module and is intended for mounting onto 144-pins edge connector sockets.

Key Features

- PC-133 support

- Auto refresh and self refresh

- 8192 refresh cycles / 64ms

- Single 3.3±0.3V power supply

- All device pins are compatible with LVTTL interface

- Data mask function by DQM

- Serial Presence Detect with EEPROM

- Module bank : two physical bank

- PCB : BSS960,Height (31.75mm),double sided component, Six layers