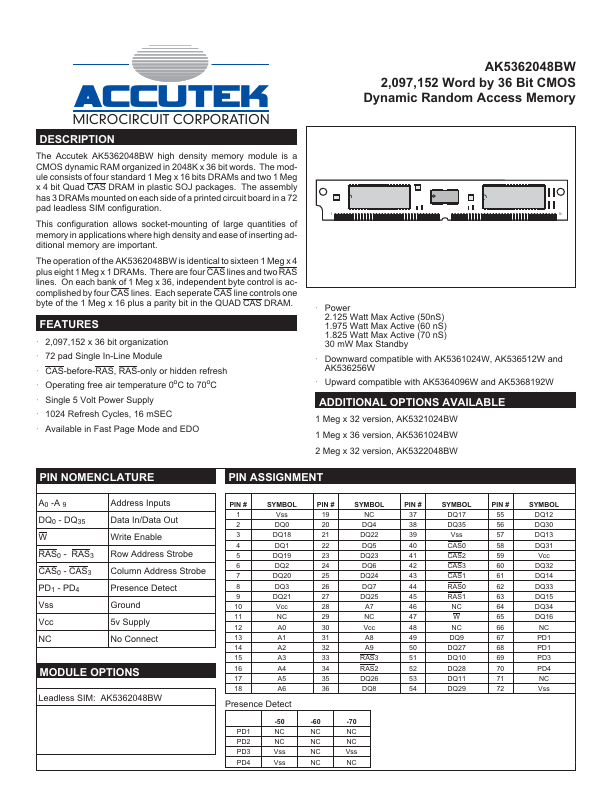

AK5362048BW

Description

The Accutek AK5362048BW high density memory module is a CMOS dynamic RAM organized in 2048K x 36 bit words. The module consists of four standard 1 Meg x 16 bits DRAMs and two 1 Meg x 4 bit Quad CAS DRAM in plastic SOJ packages.

Key Features

- 2,097,152 x 36 bit organization

- 72 pad Single In-Line Module

- CAS-before-RAS, RAS-only or hidden refresh

- Operating free air temperature 0oC to 70oC

- Single 5 Volt Power Supply

- 1024 Refresh Cycles, 16 mSEC

- Available in Fast Page Mode and EDO

- Power 2.125 Watt Max Active (50nS) 1.975 Watt Max Active (60 nS) 1.825 Watt Max Active (70 nS) 30 mW Max Standby

- Downward compatible with AK5361024W, AK536512W and AK536256W

- Upward compatible with AK5364096W and AK5368192W