AK8181C

AK8181C is 3.3V LVPECL 1:2 Clock Fanout Buffer manufactured by Asahi Kasei Microdevices.

Features

Two differential 3.3V LVPECL outputs Selectable two LVTTL/LVCMOS inputs Clock output frequency up to 266MHz Output skew : 20ps maximum Part-to-part skew : 200ps maximum Propagation delay : 1.4ns maximum Additive phase jitter(RMS) : 0.03ps(typical) Operating Temperature Range: -40 to +85℃ Package: 14-pin TSSOP (Pb free) Pin patible with ICS8535I-21

Description

The AK8181C is a member of AKM’s LVPECL clock fanout buffer family designed for tele, networking and puter applications, requiring a range of clocks with high performance and low skew. The AK8181C distributes 2 buffered clocks. AK8181C are derived from AKM’s long-termexperienced clock device technology, and enable clock output to perform low skew. The AK8181C is available in a 14-pin TSSOP package.

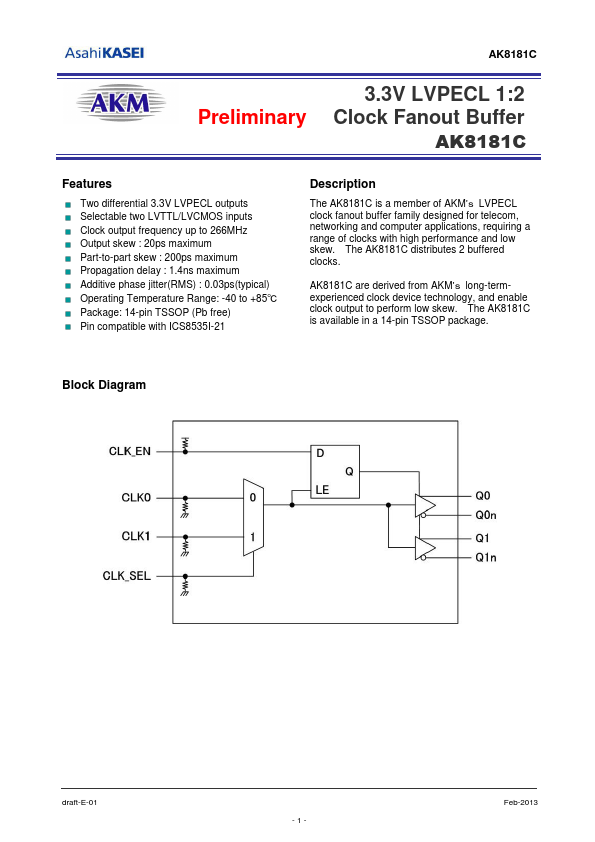

Block Diagram draft-E-01 -1-

Feb-2013 http://..

Pin Descriptions

Package: 14-Pin TSSOP(Top View)

Pin No. 1

Pin Name VSS

Pin Type PWR

Pullup down --Negative power supply

Description

CLK_EN

Pull up

Synchronizing clock output enable (LVCMOS/LVTTL) Pin is connected to VDD by internal resistor. (typ. 51kΩ) High (Open): clock outputs follow clock input. Low: Q outputs are forced low, Qn outputs are forced high. CLK Select Input (LVCMOS/LVTTL) Pin is connected to VSS by internal resistor. (typ. 51k Ω) High: selects CLK1 input Low (Open): selects CLK0 input LVCMOS/LVTTL Clock Input Pin is connected to VSS by internal resistor. (typ. 51kΩ)

- When using CLK1 input (CLK_SEL=High),it should be connected to VSS or opened. Negative power supply LVCMOS/LVTTL Clock Input Pin is connected to VSS by internal resistor. (typ. 51k Ω)

- When using CLK0 input (CLK_SEL=Low), it should be connected to VSS or opened. Positive power supply Positive power supply Differential clock output (LVPECL) No connect Differential clock output (LVPECL) Positive power supply

CLK_SEL

Pull down

CLK0

Pull down

---

CLK1

Pill down

7 8 9,10 11 12, 13 14

VDD VDD Q1n, Q1 NC Q0n, Q0...