AK8181E

AK8181E is 3.3V LVPECL 1:4 Clock Fanout Buffer manufactured by Asahi Kasei Microdevices.

Features

Four differential 3.3V LVPECL outputs Selectable crystal or differential clock inputs Clock output frequency up to 650MHz Translates any single-ended input signal to 3.3V LVPECL levels with resistor bias on PCLKn input Output skew : 10ps (typical) Part-to-part skew : 150ps (maximum) Propagation delay : 0.9ns (typical) Additive phase jitter(RMS): PCLKp/n@156.25MHz : 0.04ps (typical) XTAL@50MHz : 0.14ps (typical) Operating Temperature Range: -40 to +85℃ Package: 20-pin TSSOP (Pb free) Pin patible with ICS8533I-31

Description

The AK8181E is a member of AKM’s LVPECL clock fanout buffer family designed for tele, networking and puter applications, requiring a range of clocks with high performance and low skew. The AK8181E distributes 4 buffered clocks. AK8181E are derived from AKM’s long-termexperienced clock device technology, and enable clock output to perform low skew. The AK8181E is available in a 20-pin TSSOP package.

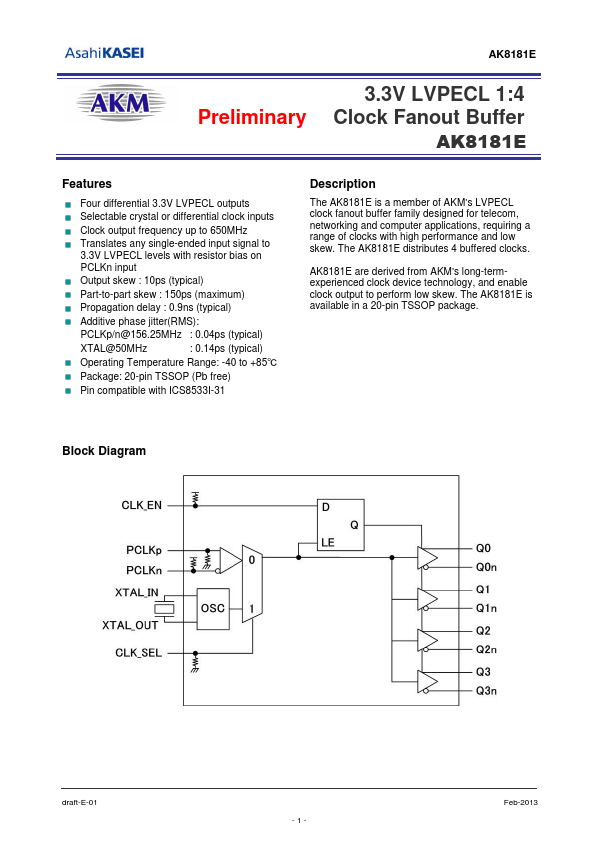

Block Diagram draft-E-01 -1-

Feb-2013 http://..

Pin Descriptions

Package: 20-Pin TSSOP(Top View)

Pin No. 1 Pin Name VSS Pin Type PWR Pullup Down --Negative power supply Synchronizing clock output enable (LVCMOS/LVTTL) 2 CLK_EN IN Pull up Pin is connected to VDD by internal resistor. (typ. 51kΩ) High(Open): clock outputs follow clock input. Low: Q outputs are forced low, Qn outputs are forced high. CLK Select Input (LVCMOS/LVTTL) 3 CLK_SEL IN Pull down Pin is connected to VSS by internal resistor. (typ. 51kΩ) High: selects XTAL inputs Low(Open): selects PCLKp/n inputs Non-inverting differential clock input Pin is connected to VSS by internal resistor. (typ. 51k Ω) Inverting differential clock input Pin is connected to VDD by internal resistor. (typ. 51kΩ) Crystal oscillator interface Crystal oscillator interface No connect No connect Positive power supply Differential clock output (LVPECL) Power supply Differential clock output (LVPECL) Differential clock output (LVPECL) Positive power supply Differential clock output (LVPECL)...