S3056

S3056 is MULTI-RATE SONET/SDH CLOCK RECOVERY UNIT manufactured by AMCC.

FEATURES

- Si Ge Bi CMOS technology

- plies with Bellcore and ITU-T specifications for jitter tolerance, jitter transfer and jitter generation

- On-chip high frequency PLL with internal loop filter for clock recovery

- Supports clock recovery for: OC-48 (2488.32 Mbps), Fibre Channel (2125 Mbps), OC-24 (1244.16 Mbps), Gigabit Ethernet (1250 Mbps), Fibre Channel (1062.5 Mbps), OC-12 (622.08 Mbps), OC-3 (155.52 Mbps) NRZ data

- Selectable reference frequencies 19.44 MHz or 155.52 MHz (or equivalent Fibre Channel/ Gigabit Ethernet frequencies)

- Lock detect- monitors frequency of ining data

- Low-jitter serial interface

- +3.3 V supply

- pact 48 pin TQFP TEP package

- Typical power 620 m W

GENERAL DESCRIPTION

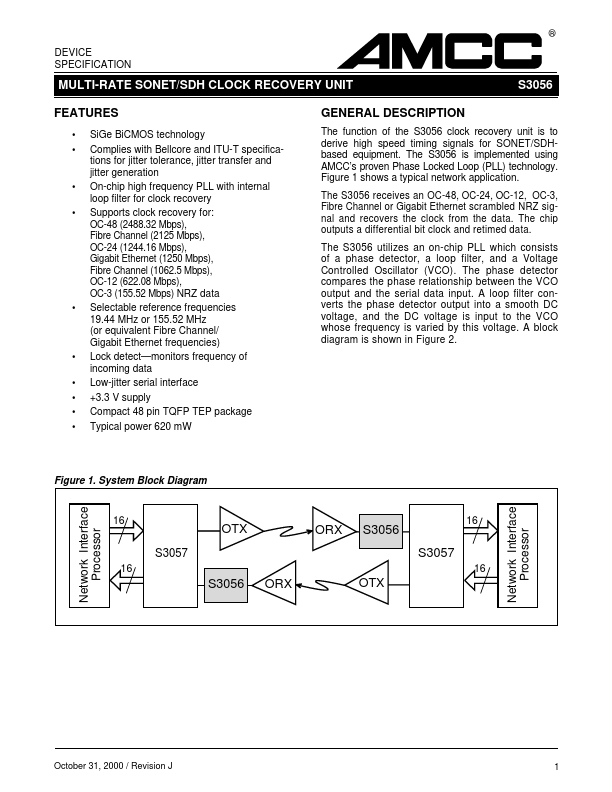

The function of the S3056 clock recovery unit is to derive high speed timing signals for SONET/SDHbased equipment. The S3056 is implemented using AMCC’s proven Phase Locked Loop (PLL) technology. Figure 1 shows a typical network application.

The S3056 receives an OC-48, OC-24, OC-12, OC-3, Fibre Channel or Gigabit Ethernet scrambled NRZ signal and recovers the clock from the data. The chip outputs a differential bit clock and retimed data.

The S3056 utilizes an on-chip PLL which consists of a phase detector, a loop filter, and a Voltage Controlled Oscillator (VCO). The phase detector pares the phase relationship between the VCO output and the serial data input. A loop filter converts the phase detector output into a smooth DC voltage, and the DC voltage is input to the VCO whose frequency is varied by this voltage. A block diagram is shown in Figure 2.

Figure 1. System Block Diagram

16 16

ORX S3056

S3057

S3056 ORX

S3057

Network Interface Processor

Network Interface Processor

October 31, 2000 / Revision J

MULTI-RATE SONET/SDH CLOCK RECOVERY UNIT

S3056 OVERVIEW

The S3056 supports clock recovery for the OC-48, Fibre Channel (2125 Mbps), OC-24, Gigabit Ethernet, Fibre Channel (1062.5 Mbps), OC-12 or OC-3 data rate. Differential serial...