S4405 Overview

Description

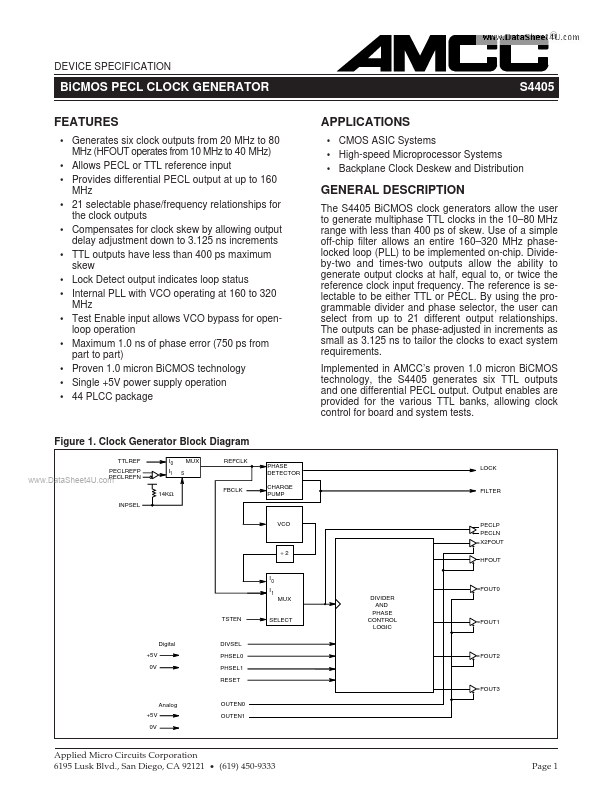

The S4405 BiCMOS clock generators allow the user to generate multiphase TTL clocks in the 10–80 MHz range with less than 400 ps of skew. Use of a simple off-chip filter allows an entire 160–320 MHz phaselocked loop (PLL) to be implemented on-chip.

Key Features

- Generates six clock outputs from 20 MHz to 80 MHz (HFOUT operates from 10 MHz to 40 MHz)

- Allows PECL or TTL reference input

- Provides differential PECL output at up to 160 MHz

- 21 selectable phase/frequency relationships for the clock outputs

- Compensates for clock skew by allowing output delay adjustment down to 3.125 ns increments

- TTL outputs have less than 400 ps maximum skew

- Lock Detect output indicates loop status

- Internal PLL with VCO operating at 160 to 320 MHz

- Test Enable input allows VCO bypass for openloop operation

- Maximum 1.0 ns of phase error (750 ps from part to part)