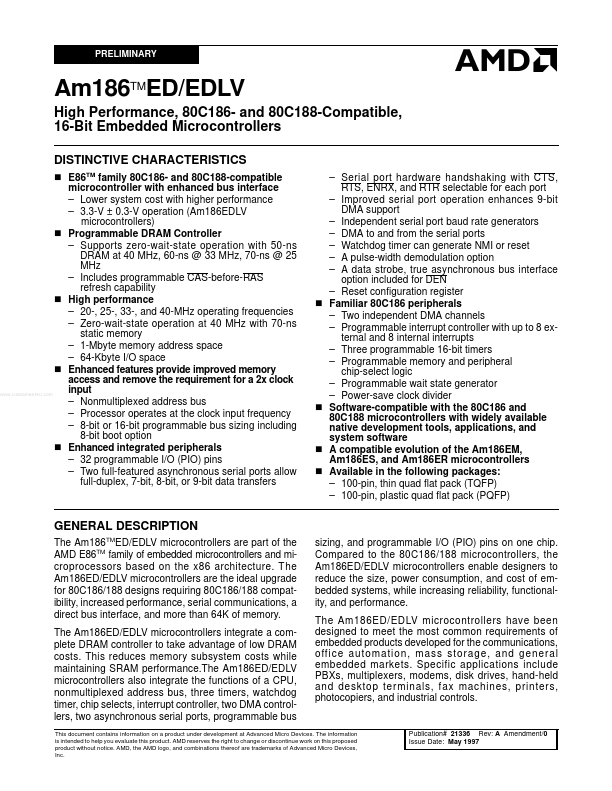

AM186EDLV

AM186EDLV is 16-Bit Embedded Microcontrollers manufactured by AMD.

- Part of the AM186ED comparator family.

- Part of the AM186ED comparator family.

features provide improved memory access and remove the requirement for a 2x clock input ..

- Nonmultiplexed address bus

- Processor operates at the clock input frequency

- 8-bit or 16-bit programmable bus sizing including 8-bit boot option n Enhanced integrated peripherals

- 32 programmable I/O (PIO) pins

- Two full-featured asynchronous serial ports allow full-duplex, 7-bit, 8-bit, or 9-bit data transfers

- Serial port hardware handshaking with CTS, RTS, ENRX, and RTR selectable for each port

- Improved serial port operation enhances 9-bit DMA support

- Independent serial port baud rate generators

- DMA to and from the serial ports

- Watchdog timer can generate NMI or reset

- A pulse-width demodulation option

- A data strobe, true asynchronous bus interface option included for DEN

- Reset configuration register Familiar 80C186 peripherals

- Two independent DMA channels

- Programmable interrupt controller with up to 8 external and 8 internal interrupts

- Three programmable 16-bit timers

- Programmable memory and peripheral chip-select logic

- Programmable wait state generator

- Power-save clock divider Software-patible with the 80C186 and 80C188 microcontrollers with widely available native development tools, applications, and system software A patible evolution of the Am186EM, Am186ES, and Am186ER microcontrollers Available in the following packages:

- 100-pin, thin quad flat pack (TQFP)

- 100-pin, plastic quad flat pack (PQFP) n

GENERAL DESCRIPTION

The Am186TMED/EDLV microcontrollers are part of the AMD E86TM family of embedded microcontrollers and microprocessors based on the x86 architecture. The Am186ED/EDLV microcontrollers are the ideal upgrade for 80C186/188 designs requiring 80C186/188 patibility, increased performance, serial munications, a direct bus interface, and more than 64K of memory. The Am186ED/EDLV microcontrollers integrate a plete DRAM controller to take advantage of low DRAM costs. This reduces memory subsystem costs while maintaining SRAM...