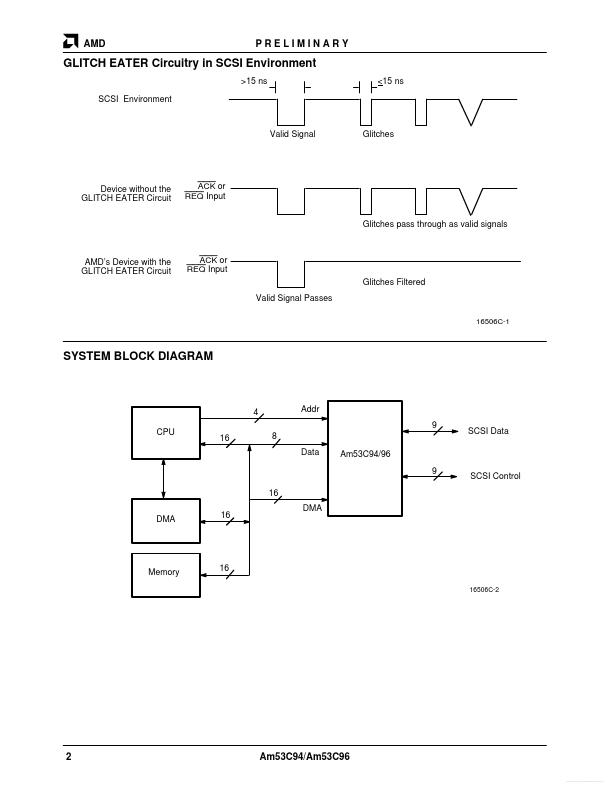

Datasheet Summary

PRELIMINARY

Am53C94/Am53C96

High Performance SCSI Controller

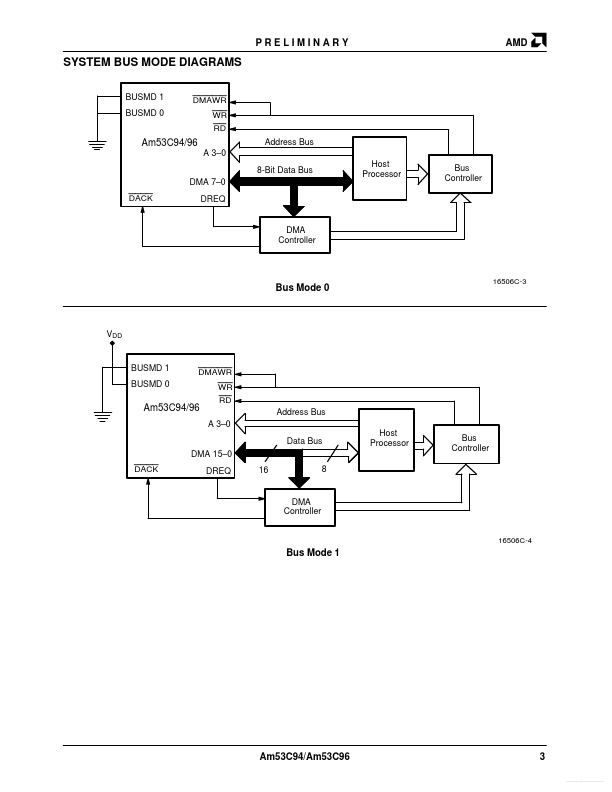

DISTINCTIVE CHARACTERISTICS s s s s s s s s s Pin/function patible with NCR53C94/53C96 AMD’s Patented GLITCH EATERTM Circuitry on REQ and ACK inputs 5 Mbytes per second synchronous SCSI transfer rate 20 Mbytes per second DMA transfer rate 16-bit DMA Interface plus 2 bits of parity Flexible three bus architecture Single ended SCSI bus supported by Am53C94 Single ended and differential SCSI bus supported by Am53C96 Selection of multiplexed or non-multiplexed address and data bus s s s s s s s s

Advanced Micro Devices

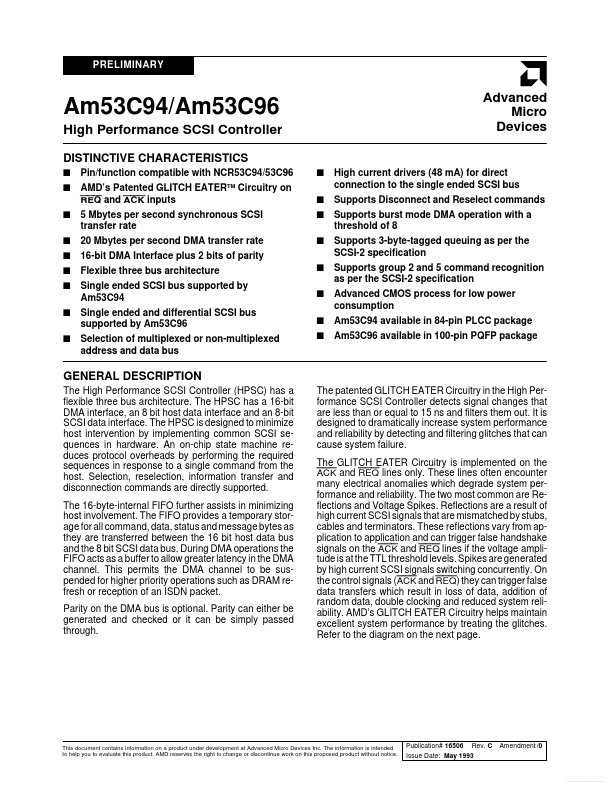

High current drivers (48 mA) for direct connection to the single ended SCSI bus Supports Disconnect and...