Am2533

Am2533 is 1024-Bit Static Shift Registers manufactured by AMD.

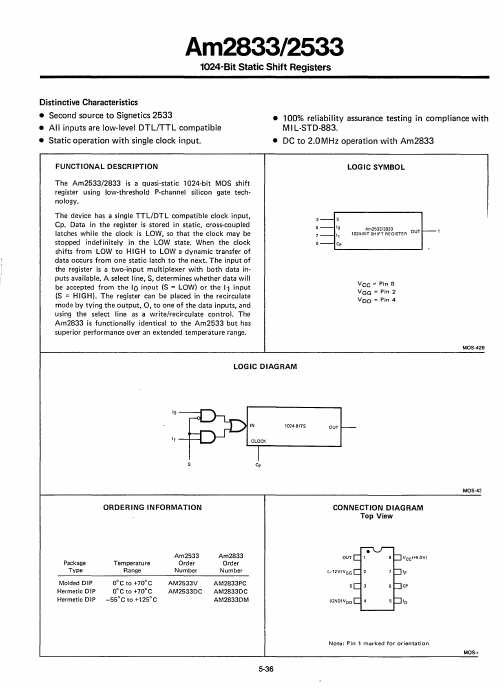

Am2833/2533

1024-Bit Static Shift Registers

Distinctive Characteristics

- Second source to Signetics 2533

- All inputs are low-level DTL/TTL patible

- Static operation with single clock input.

- 100% reliability assurance testing in pliance with M I L-STD-883 .

- DC to 2.0MHz operation with Am2833

FUNCTIONAL DESCRIPTION

The Am2533/2833 is a quasi-static 1024-bit MaS shift register using low-threshold P-channel silicon gate technology.

The device has a single TTL/DTL patible clock input, Cpo Data in the register is stored in static, cross-coupled latches while the clock is LOW, so that the clock may be stopped indefinitely in the LOW state. When the clock shifts from LOW to HIGH...