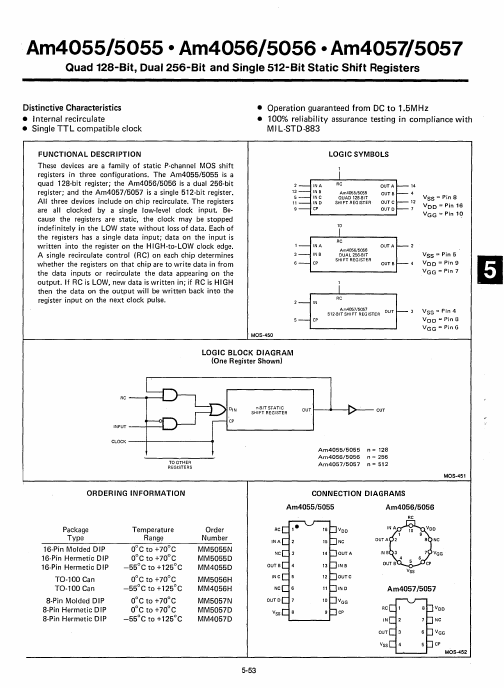

Datasheet Summary

Am4055/5055

- Am4056/5056

- Am4057/5057

Quad 128-Bit, Dual 256-Bit and Single 512-Bit Static Shift Registers

Distinctive Characteristics

- Internal recirculate

- Single TTL patible clock

- Operation guaranteed from DC to 1.5MHz

- 100% reliability assurance testing in pliance with MI L-STD-883

FUNCTIONAL DESCRIPTION

These devices are a family of static P-channel MOS shift registers in three configurations. The Am40SS/S0SS is a quad 128- bit register; the Am40S6/S0S6 is a dual 2S6- bit register; and the Am40S7/S0S7 is a single S12-bit register.

All three devices include on chip recirculate. The registers

S 11 are all clocked by a single low-level clock input. Be-

9 cause...