JK124

JK124 is CMOS Gate Array manufactured by AMI.

- Part of the JK121 comparator family.

- Part of the JK121 comparator family.

Description

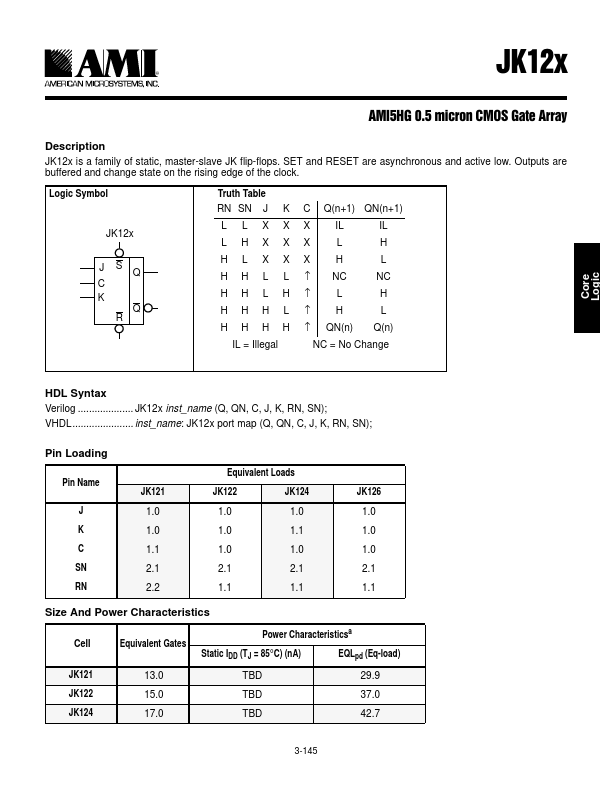

JK12x is a family of static, master-slave JK flip-flops. SET and RESET are asynchronous and active low. Outputs are buffered and change state on the rising edge of the clock.

Logic Symbol

JK12x

J SQ C K

Truth Table RN SN J K L L XX LHXX HLXX HHL L HH L H HHH L HHHH

IL = Illegal

C Q(n+1) QN(n+1)

X IL

↑ NC

↑L

↑H

↑ QN(n) Q(n)

NC = No Change

Core Logic

HDL Syntax Verilog JK12x inst_name (Q, QN, C, J, K, RN, SN); VHDL inst_name: JK12x port map (Q, QN, C, J, K, RN, SN);

Pin Loading

Pin Name

J K C SN RN

JK121 1.0 1.0 1.1 2.1 2.2

Equivalent Loads

JK122

1.0 1.0

1.0 1.1

1.0 1.0

2.1 2.1

1.1 1.1

JK126 1.0 1.0 1.0 2.1 1.1

Size And Power Characteristics

Power Characteristicsa

Cell Equivalent...