ODPSXE24

ODPSXE24 is CMOS Gate Array manufactured by AMI.

2'36;(

®

$0,+- PLFURQ &026

- DWH $UUD

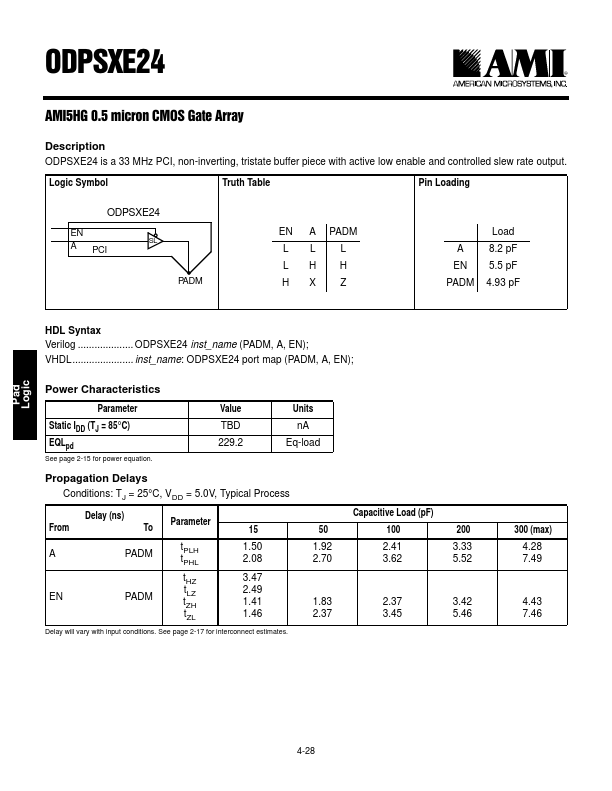

Description ODPSXE24 is a 33 MHz PCI, non-inverting, tristate buffer piece with active low enable and controlled slew rate output.

Logic Symbol

Truth Table

Pin Loading

EN A PCI

PADM

EN A PADM LL L LH H HX Z

A EN PADM

Load 8.2 pF 5.5 pF 4.93 pF

HDL Syntax Verilog .................... ODPSXE24 inst_name (PADM, A, EN); VHDL...................... inst_name: ODPSXE24 port map (PADM, A, EN);

Power Characteristics

Parameter Static IDD (TJ = 85°C) EQLpd

See page 2-15 for power equation.

Value TBD 229.2

Units nA Eq-load

Propagation Delays Conditions: TJ = 25°C, VDD = 5.0V, Typical Process

Delay (ns) From

To...