Datasheet Summary

2M X 16 Bit X 4 Banks Synchronous DRAM

Document Title 2M X 16 Bit X 4 Banks Synchronous DRAM

Revision History

Rev. No.

0.0 1.0 2.0 3.0 3.1 3.2

History

Initial issue Add -6, -7 spec. Add -V grade Add Full Page Mode Add CL2 parameters Add Pb-Free package type

Issue Date

August 9, 2001 October 3, 2001 November 26,2001 February 21, 2002 December 12, 2003 September 2, 2004

Remark

(September, 2004, Version 3.2)

AMIC Technology, Corp.

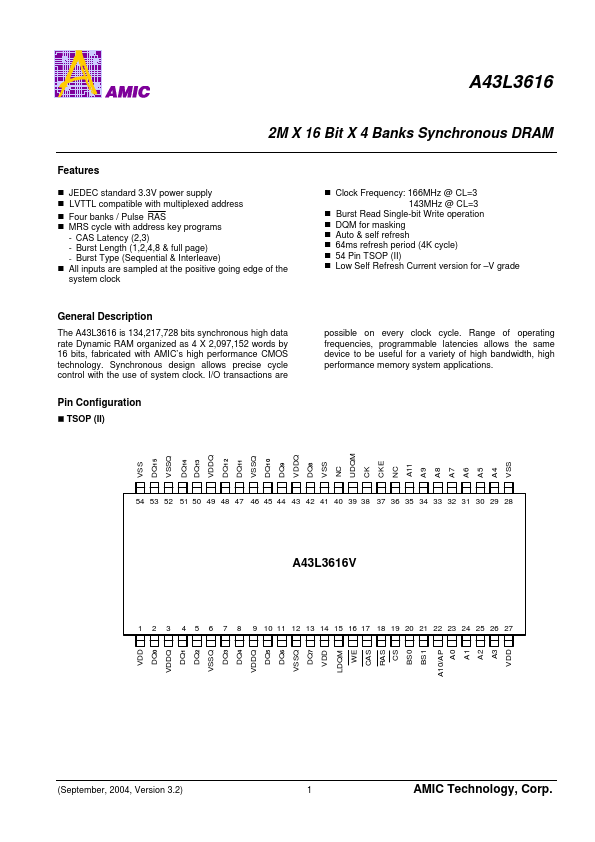

2M X 16 Bit X 4 Banks Synchronous DRAM

Features

JEDEC standard 3.3V power supply LVTTL patible with multiplexed address

Four banks / Pulse RAS MRS cycle with address key programs

- CAS Latency (2,3)

- Burst Length (1,2,4,8 & full...