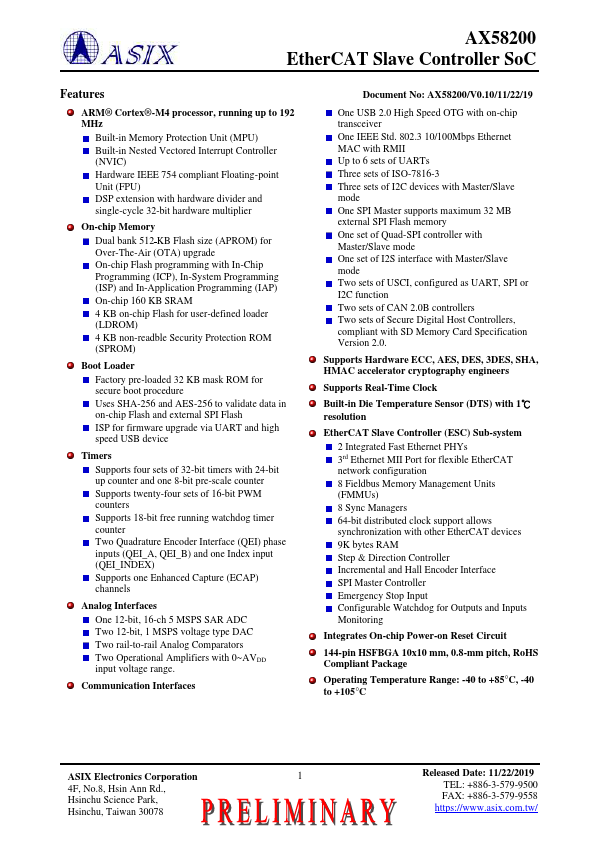

| Part | AX58200 |

|---|---|

| Description | EtherCAT Slave Controller SoC |

| Manufacturer | ASIX |

| Size | 4.55 MB |

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| No distributor offers were returned for this part. | |||

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| IP5328P | Injoinic | Fully-Integrated Bi-directional PD3.0 and Fast Charge Power-Bank SOC |

| IP5513 | Injoinic | TWS Bluetooth Earphone Charging Box SOC |

| IP5416 | Injoinic | TWS Bluetooth Earphone Charging Box SOC |