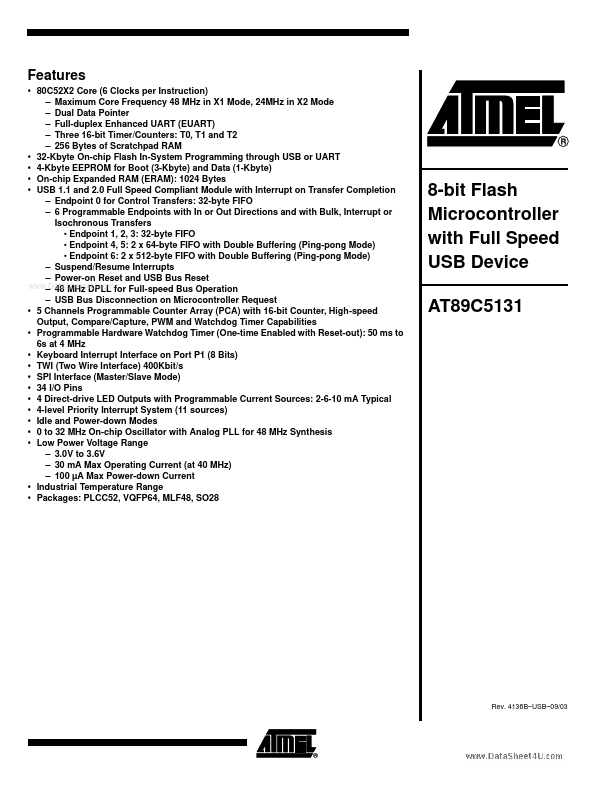

89C5131

Description

AT89C5131 is a high-performance Flash version of the 80C51 single-chip 8-bit microcontrollers with full speed USB functions. AT89C5131 features a full-speed USB module compatible with the USB specifications Version 1.1 and 2.0.

Key Features

- 80C52X2 Core (6 Clocks per Instruction) - Maximum Core Frequency 48 MHz in X1 Mode, 24MHz in X2 Mode - Dual Data Pointer - Full-duplex Enhanced UART (EUART) - Three 16-bit Timer/Counters: T0, T1 and T2 - 256 Bytes of Scratchpad RAM

- 32-Kbyte On-chip Flash In-System Programming through USB or UART

- 4-Kbyte EEPROM for Boot (3-Kbyte) and Data (1-Kbyte)

- On-chip Expanded RAM (ERAM): 1024 Bytes

- USB 1.1 and 2.0 Full Speed Compliant Module with Interrupt on Transfer Completion - Endpoint 0 for Control Transfers: 32-byte FIFO - 6 Programmable Endpoints with In or Out Directions and with Bulk, Interrupt or Isochronous Transfers

- Endpoint 1, 2, 3: 32-byte FIFO

- Endpoint 4, 5: 2 x 64-byte FIFO with Double Buffering (Ping-pong Mode)

- 5 Channels Programmable Counter Array (PCA) with 16-bit Counter, High-speed Output, Compare/Capture, PWM and Watchdog Timer Capabilities

- Programmable Hardware Watchdog Timer (One-time Enabled with Reset-out): 50 ms to 6s at 4 MHz

- Keyboard Interrupt Interface on Port P1 (8 Bits)