AT83EC5136

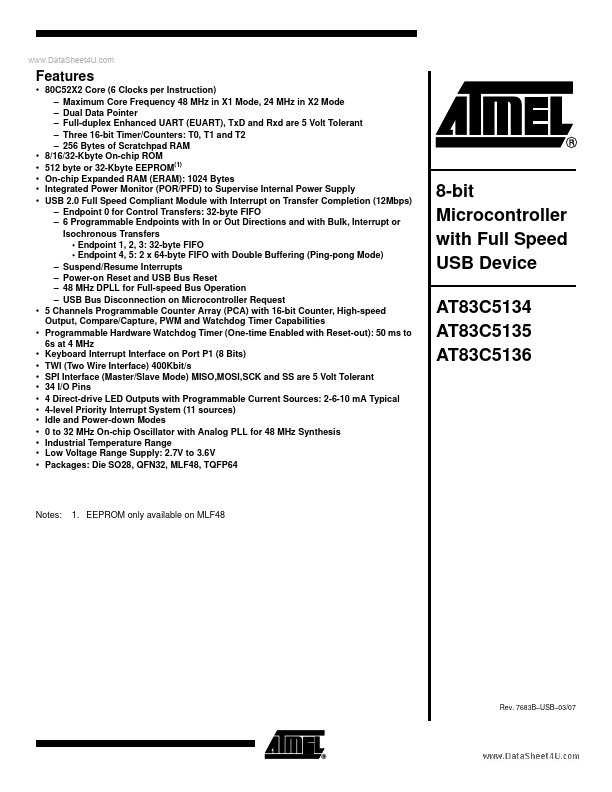

Key Features

- 80C52X2 Core (6 Clocks per Instruction) - Maximum Core Frequency 48 MHz in X1 Mode, 24 MHz in X2 Mode - Dual Data Pointer - Full-duplex Enhanced UART (EUART), TxD and Rxd are 5 Volt Tolerant - Three 16-bit Timer/Counters: T0, T1 and T2 - 256 Bytes of Scratchpad RAM 8/16/32-Kbyte On-chip ROM 512 byte or 32-Kbyte EEPROM(1) On-chip Expanded RAM (ERAM): 1024 Bytes Integrated Power Monitor (POR/PFD) to Supervise Internal Power Supply USB 2.0 Full Speed Compliant Module with Interrupt on Transfer Completion (12Mbps) - Endpoint 0 for Control Transfers: 32-byte FIFO - 6 Programmable Endpoints with In or Out Directions and with Bulk, Interrupt or Isochronous Transfers

- Endpoint 1, 2, 3: 32-byte FIFO

- Endpoint 4, 5: 2 x 64-byte FIFO with Double Buffering (Ping-pong Mode) - Suspend/Resume Interrupts - Power-on Reset and USB Bus Reset - 48 MHz DPLL for Full-speed Bus Operation - USB Bus Disconnection on Microcontroller Request 5 Channels Programmable Counter Array (PCA) with 16-bit Counter, High-speed Output, Compare/Capture, PWM and Watchdog Timer Capabilities Programmable Hardware Watchdog Timer (One-time Enabled with Reset-out): 50 ms to 6s at 4 MHz Keyboard Interrupt Interface on Port P1 (8 Bits) TWI (Two Wire Interface) 400Kbit/s SPI Interface (Master/Slave Mode) MISO,MOSI,SCK and SS are 5 Volt Tolerant 34 I/O Pins 4 Direct-drive LED Outputs with Programmable Current Sources: 2-6-10 mA Typical 4-level Priority Interrupt System (11 sources) Idle and Power-down Modes 0 to 32 MHz On-chip Oscillator with Analog PLL for 48 MHz Synthesis Industrial Temperature Range Low Voltage Range Supply: 2.7V to 3.6V Packages: Die SO28, QFN32, MLF48, TQFP64 * * * *

- 8-bit Microcontroller with Full Speed USB Device AT83C5134 AT83C5135 AT83C5136 * * * * * * * * * * * *

- Notes:

- EEPROM only available on MLF48 Rev. 7683B-USB-03/07