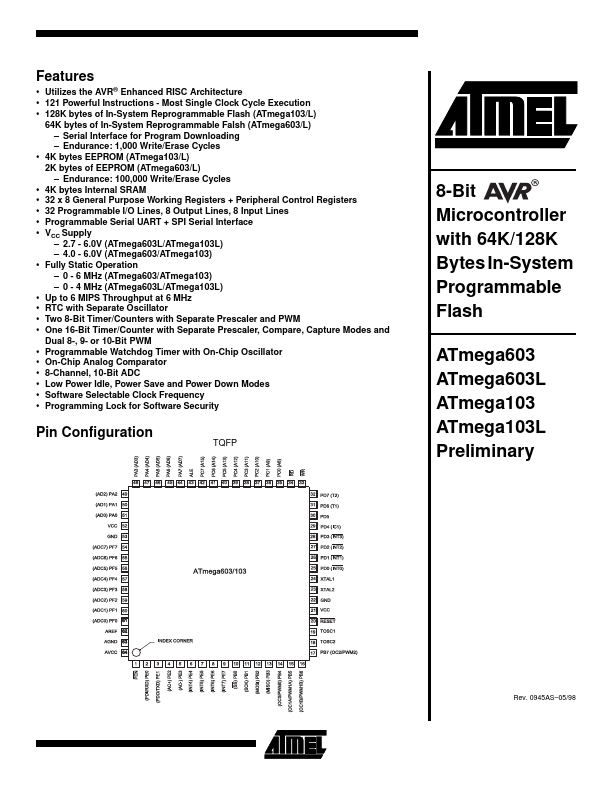

ATMEGA603L

Features

- Utilizes the AVR® Enhanced RISC Architecture

- 121 Powerful Instructions

- Most Single Clock Cycle Execution

- 128K bytes of In-System Reprogrammable Flash (ATmega103/L)

64K bytes of In-System Reprogrammable Falsh (ATmega603/L)

- Serial Interface for Program Downloading

- Endurance: 1,000 Write/Erase Cycles 4K bytes EEPROM (ATmega103/L) 2K bytes of EEPROM (ATmega603/L)

- Endurance: 100,000 Write/Erase Cycles 4K bytes Internal SRAM 32 x 8 General Purpose Working Registers + Peripheral Control Registers 32 Programmable I/O Lines, 8 Output Lines, 8 Input Lines Programmable Serial UART + SPI Serial Interface VCC Supply

- 2.7

- 6.0V (ATmega603L/ATmega103L)

- 4.0

- 6.0V (ATmega603/ATmega103) Fully Static Operation

- 0

- 6 MHz (ATmega603/ATmega103)

- 0

- 4 MHz (ATmega603L/ATmega103L) Up to 6 MIPS Throughput at 6 MHz RTC with Separate Oscillator Two 8-Bit Timer/Counters with Separate Prescaler and PWM One 16-Bit Timer/Counter with Separate Prescaler, pare, Capture Modes and Dual...