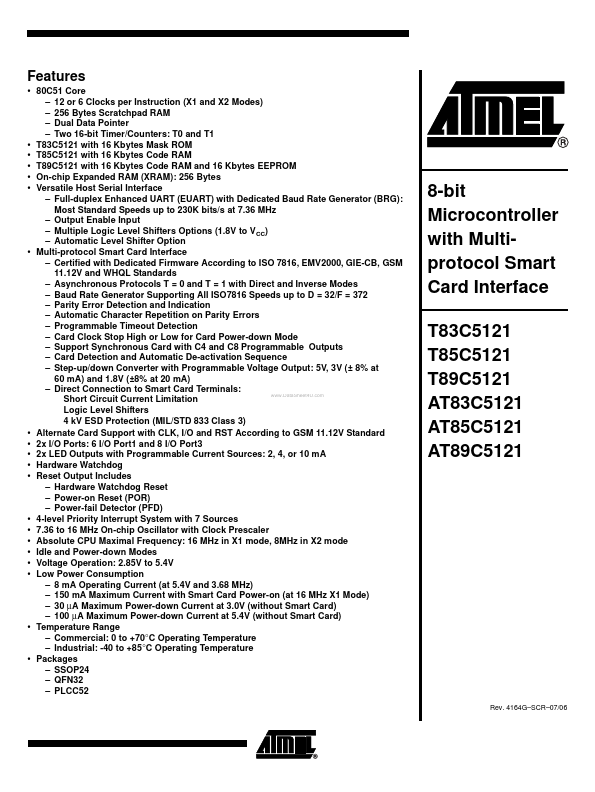

T85C5121

Features

- 80C51 Core

- 12 or 6 Clocks per Instruction (X1 and X2 Modes)

- 256 Bytes Scratchpad RAM

- Dual Data Pointer

- Two 16-bit Timer/Counters: T0 and T1 T83C5121 with 16 Kbytes Mask ROM T85C5121 with 16 Kbytes Code RAM T89C5121 with 16 Kbytes Code RAM and 16 Kbytes EEPROM On-chip Expanded RAM (XRAM): 256 Bytes Versatile Host Serial Interface

- Full-duplex Enhanced UART (EUART) with Dedicated Baud Rate Generator (BRG): Most Standard Speeds up to 230K bits/s at 7.36 MHz

- Output Enable Input

- Multiple Logic Level Shifters Options (1.8V to V CC)

- Automatic Level Shifter Option Multi-protocol Smart Card Interface

- Certified with Dedicated Firmware According to ISO 7816, EMV2000, GIE-CB, GSM 11.12V and WHQL Standards

- Asynchronous Protocols T = 0 and T = 1 with Direct and Inverse Modes

- Baud Rate Generator Supporting All ISO7816 Speeds up to D = 32/F = 372

- Parity Error Detection and Indication

- Automatic Character Repetition on Parity Errors

- Programmable Timeout Detection

-...