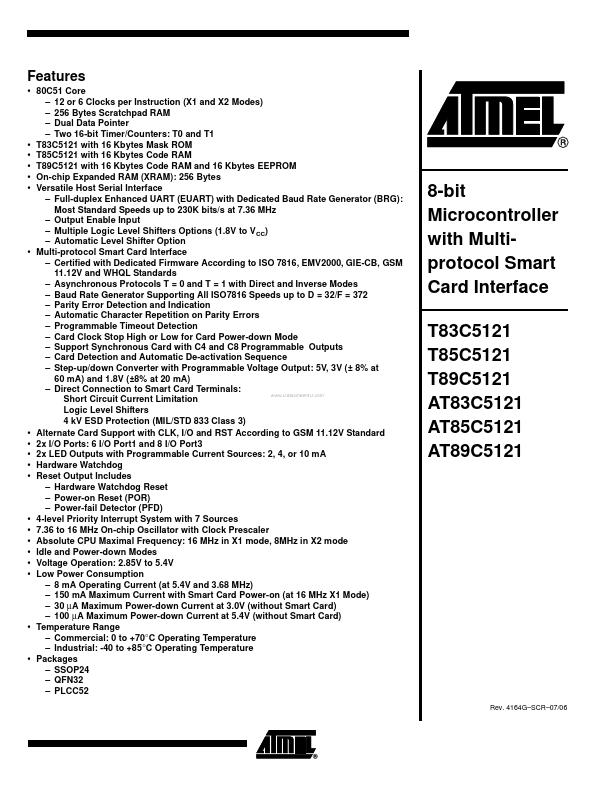

| Part | T89C5121 |

|---|---|

| Description | 8-bit Microcontroller |

| Category | Microcontroller |

| Manufacturer | Atmel |

| Size | 864.85 KB |

Pricing from 8.63 USD, available from DigiKey and Win Source.

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| DigiKey | 1095 | 1+ : 8.63 USD 10+ : 7.153 USD 59+ : 6.26085 USD 118+ : 5.98534 USD |

View Offer |

| Win Source | 1500 | 7+ : 9.3806 USD 16+ : 7.6969 USD 24+ : 7.4564 USD 33+ : 7.2159 USD |

View Offer |

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| ATmega328P | Atmel | 8-bit Microcontroller |

| TMPM375FSDMG | Toshiba | 32-Bit RISC Microcontroller |

| CH32V003 | WCH | Microcontroller |