TSPC860 Description

The TSPC860 PowerPC QUad Integrated munication Controller (Power QUICC®) is a versatile one-chip integrated microprocessor and peripheral bination that can be used in a variety of controller applications. It particularly excels in munications and networking systems. The Power QUICC (pronounced “quick”) can be described as a PowerPC-based derivative of the TS68EN360 (QUICC™).

TSPC860 Key Features

- PowerPC® Single Issue Integer Core

- Precise Exception Model

- Extensive System Development Support

- On-chip Watchpoints and Breakpoints

- Program Flow Tracking

- On-chip Emulation (Once) Development Interface

- High Performance (Dhrystone 2.1: 52 MIPS at 50 MHz, 3.3V, 1.3 Watts Total Power)

- Low Power (< 241 mW at 25 MHz, 2.4V Internal, 3.3V I/O-core, Caches, MMUs, I/O)

- MPC8XX PowerPC System Interface, Including a Periodic Interrupt Timer, a Bus Monitor, and Real-time Clocks

- Single Issue, 32-bit Version of the Embedded PowerPC Core (Fully patible with Book 1 of the PowerPC Architecture Definit

TSPC860 Applications

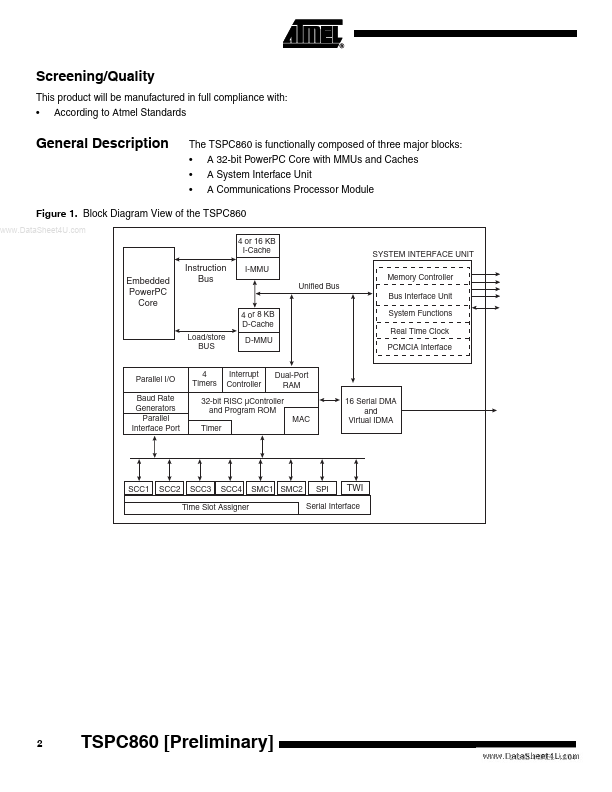

- According to Atmel Standards The TSPC860 is functionally posed of three major blocks