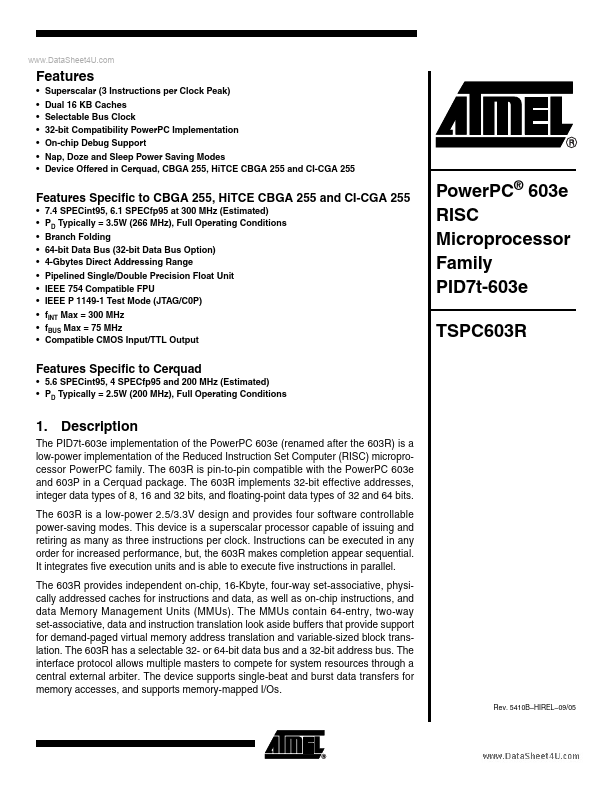

TSXPC603R

TSXPC603R is PowerPC 603e RISC Microprocessor Family PID7t-603e manufactured by Atmel.

Features

- -

- -

- -

- Superscalar (3 Instructions per Clock Peak) Dual 16 KB Caches Selectable Bus Clock 32-bit patibility Power PC Implementation On-chip Debug Support Nap, Doze and Sleep Power Saving Modes Device Offered in Cerquad, CBGA 255, Hi TCE CBGA 255 and CI-CGA 255

Features

Specific to CBGA 255, Hi TCE CBGA 255 and CI-CGA 255

- -

- -

- -

- -

- -

- 7.4 SPECint95, 6.1 SPECfp95 at 300 MHz (Estimated) PD Typically = 3.5W (266 MHz), Full Operating Conditions Branch Folding 64-bit Data Bus (32-bit Data Bus Option) 4-Gbytes Direct Addressing Range Pipelined Single/Double Precision Float Unit IEEE 754 patible FPU IEEE P 1149-1 Test Mode (JTAG/C0P) f INT Max = 300 MHz f BUS Max = 75 MHz patible CMOS Input/TTL Output

Power PC® 603e RISC Microprocessor Family PID7t-603e TSPC603R

Features

Specific to Cerquad

- 5.6 SPECint95, 4 SPECfp95 and 200 MHz (Estimated)

- PD Typically = 2.5W (200 MHz), Full Operating Conditions

1. Description

The PID7t-603e implementation of the Power PC 603e (renamed after the 603R) is a low-power implementation of the Reduced Instruction Set puter (RISC) microprocessor Power PC family. The 603R is pin-to-pin patible with the Power PC 603e and 603P in a Cerquad package. The 603R implements 32-bit effective addresses, integer data types of 8, 16 and 32 bits, and floating-point data types of 32 and 64 bits. The 603R is a low-power 2.5/3.3V design and provides four software controllable power-saving modes. This device is a superscalar processor capable of issuing and retiring as many as three instructions per clock. Instructions can be executed in any order for increased performance, but, the 603R makes pletion appear sequential. It integrates five execution units and is able to execute five instructions in parallel. The 603R provides independent on-chip, 16-Kbyte, four-way set-associative, physically addressed caches for instructions and data, as well as on-chip instructions, and data Memory Management Units (MMUs). The MMUs contain 64-entry,...