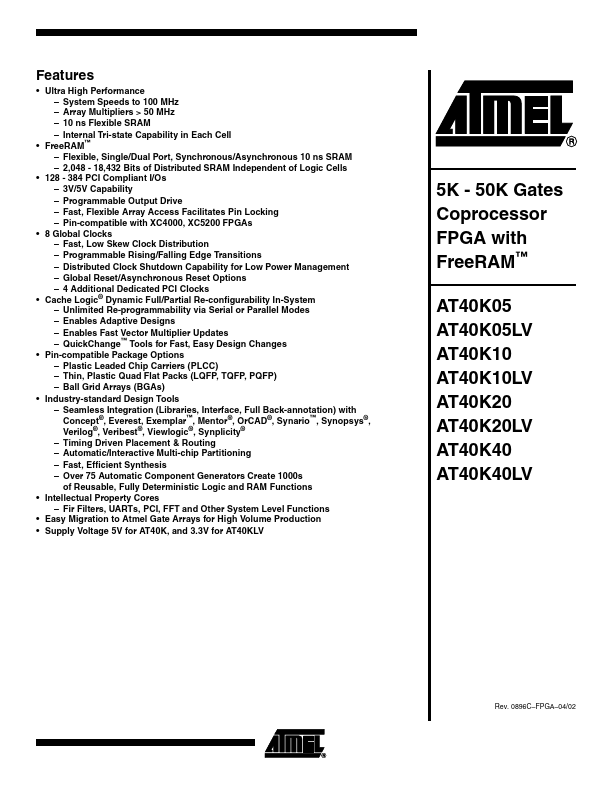

AT40K20LV

AT40K20LV is 5K - 50K Gates Coprocessor FPGA manufactured by Atmel.

Features

- Ultra High Performance

- System Speeds to 100 MHz

- Array Multipliers > 50 MHz

- 10 ns Flexible SRAM

- Internal Tri-state Capability in Each Cell

- FreeRAM™

- Flexible, Single/Dual Port, Synchronous/Asynchronous 10 ns SRAM

- 2,048

- 18,432 Bits of Distributed SRAM Independent of Logic Cells

- 128

- 384 PCI pliant I/Os

- 3V/5V Capability

- Programmable Output Drive

- Fast, Flexible Array Access Facilitates Pin Locking

- Pin-patible with XC4000, XC5200 FPGAs

- 8 Global Clocks

- Fast, Low Skew Clock Distribution

- Programmable Rising/Falling Edge Transitions

- Distributed Clock Shutdown Capability for Low Power Management

- Global Reset/Asynchronous Reset Options

- 4...