Datasheet Summary

Features

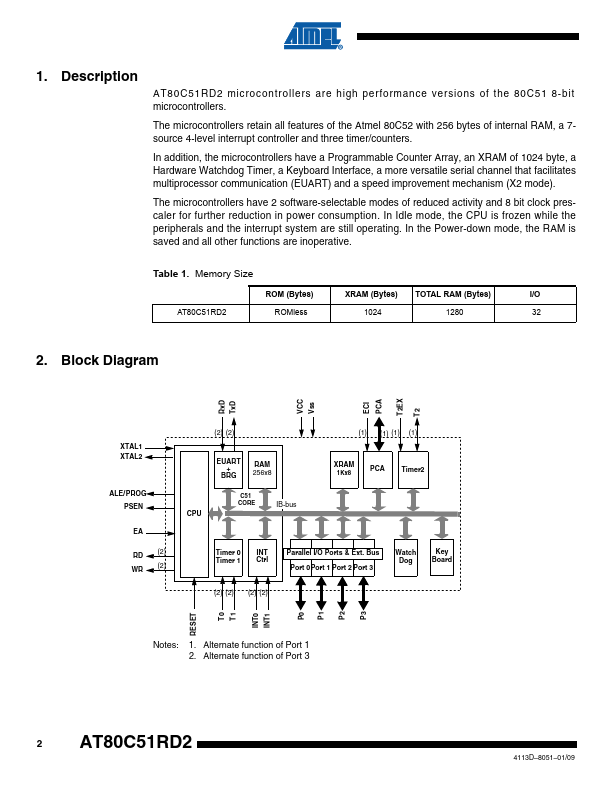

- 80C52 patible

- Four 8-bit I/O Ports

- Three 16-bit Timer/Counters

- 256 Bytes Scratch Pad RAM

- 8 Interrupt Sources with 4 Priority Levels

- Dual Data Pointer

- Variable Length MOVX for Slow RAM/Peripherals

- High-speed Architecture

- 10 to 40 MHz in Standard Mode

- 16K/32K Bytes On-Chip ROM Program

- AT80C51RD2 ROMless Versions

- On-Chip 1024 bytes Expanded RAM (XRAM)

- Software Selectable Size (0, 256, 512, 768, 1024 bytes)

- 256 Bytes Selected at Reset

- Keyboard Interrupt Interface on Port P1

- 8-bit Clock Prescaler

- 64K Program and Data Memory Spaces

- Improved X2 Mode with Independant Selection for CPU and Each Peripheral

- Programmable Counter Array 5 Channels with:

-...