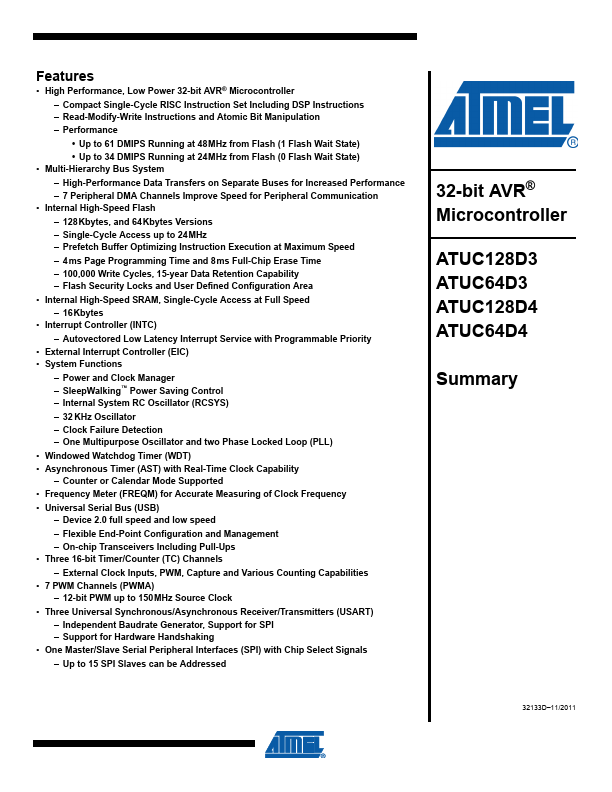

ATUC128D4

ATUC128D4 is 32-bit AVR Microcontroller manufactured by Atmel.

- Part of the ATUC128D3 comparator family.

- Part of the ATUC128D3 comparator family.

Features

- High Performance, Low Power 32-bit AVR® Microcontroller

- pact Single-Cycle RISC Instruction Set Including DSP Instructions

- Read-Modify-Write Instructions and Atomic Bit Manipulation

- Performance

- Up to 61 DMIPS Running at 48MHz from Flash (1 Flash Wait State)

- Up to 34 DMIPS Running at 24MHz from Flash (0 Flash Wait State)

- Multi-Hierarchy Bus System

- High-Performance Data Transfers on Separate Buses for Increased Performance

- 7 Peripheral DMA Channels Improve Speed for Peripheral munication

- Internal High-Speed Flash

- 128Kbytes, and 64Kbytes Versions

- Single-Cycle Access up to 24MHz

- Prefetch Buffer Optimizing Instruction Execution at Maximum Speed

- 4ms Page...