PC755

PC755 is 32-bit RISC Microprocessor manufactured by Atmel.

Features

- 18.1SPECint95, Estimates 12.3 SPECfp95 at 400 MHz (PC755)

- 15.7SPECint95, 9SPECfp95 at 350 MHz (PC745)

- 733 MIPS at 400 MHz (PC755) at 641 MIPS at 350 MHz (PC745)

- Selectable Bus Clock (12 CPU Bus Dividers up to 10x)

- PD Typical 6.4W at 400 MHz, Full Operating Conditions

- Nap, Doze and Sleep Modes for Power Savings

- Superscalar (3 Instructions per Clock Cycle) Two Instruction + Branch

- 4 Beta Byte Virtual Memory, 4-GByte of Physical Memory

- 64-bit Data and 32-bit Address Bus Interface

- 32-KB Instruction and Data Cache

- Six Independent Execution Units

- Write-back and Write-through Operations

- f INT max = 400 MHz (TBC)

- f BUS max = 100 MHz

- Voltage I/O 2.5V/3.3V; Voltage Int 2.0V

Power PC 755/745 32-bit RISC Microprocessor

Description

The PC755 and PC745 Power PC® microprocessors are high-performance, lowpower, 32-bit implementations of the Power PC Reduced Instruction Set puter (RISC) architecture, especially enhanced for embedded applications.

The PC755 and PC745 microprocessors differ only in that the PC755 Features an enhanced, dedicated L2 cache interface with on-chip L2 tags. The PC755 is a drop-in replacement for the award winning Power PC 750 microprocessor and is footprint and user software code patible with the MPC7400 microprocessor with Alti Vec technology. The PC745 is a drop-in replacement for the Power PC 740 microprocessor and is also footprint and user software code patible with the Power PC 603e microprocessor. PC755/745 microprocessors provide on-chip debug support and are fully JTAG-pliant.

The PC745 microprocessor is pin patible with the TSPC603e family.

PC755/745

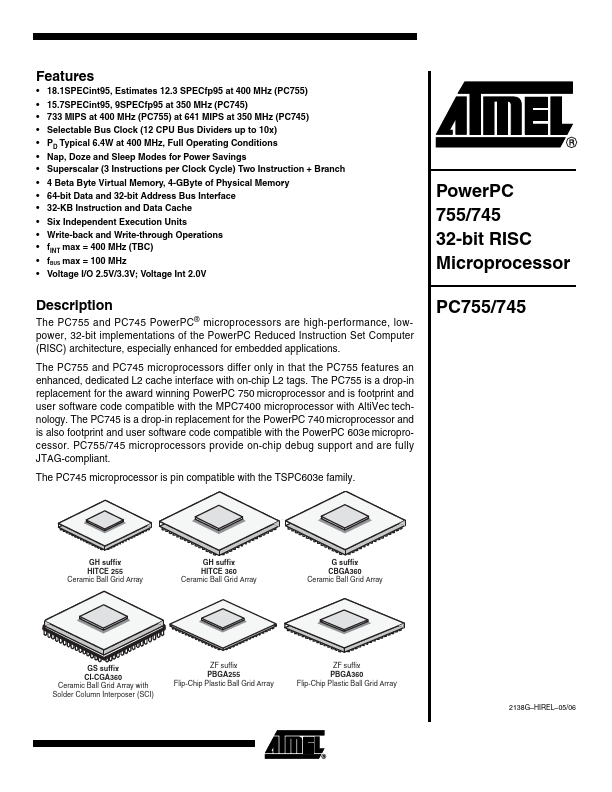

GH suffix HITCE 255 Ceramic Ball Grid Array

GH suffix HITCE 360 Ceramic Ball Grid Array

G suffix CBGA360 Ceramic Ball Grid Array

GS suffix CI-CGA360 Ceramic Ball Grid Array with Solder Column Interposer (SCI)

ZF suffix PBGA255 Flip-Chip Plastic Ball Grid Array

ZF suffix PBGA360 Flip-Chip Plastic Ball Grid Array

2138G- HIREL- 05/06

Screening...