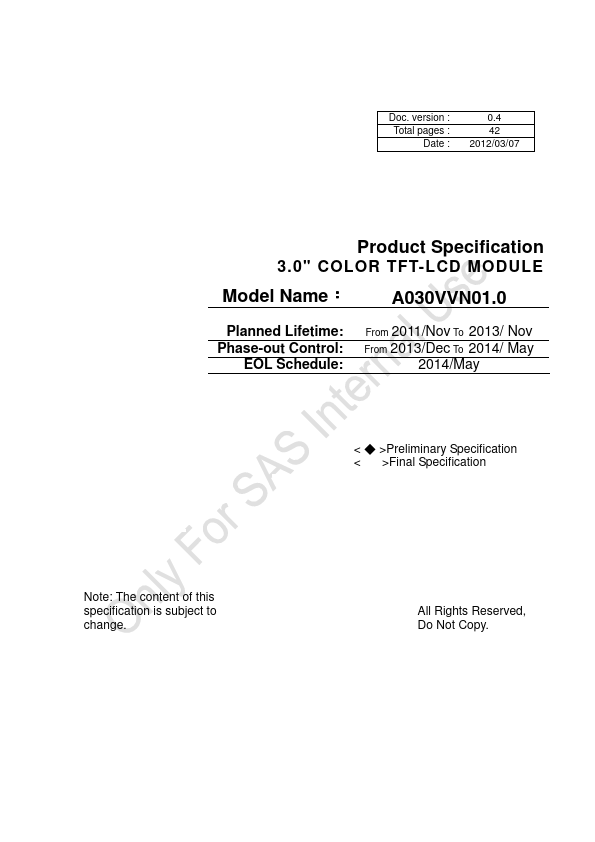

A030VVN01.0 Overview

Description

Ground 2 DR7 I Data signal (MSB) 3 DR6 I Data signal 4 DR5 I Data signal 5 DR4 I Data signal 6 DR3 I Data signal 7 DR2 I Data signal 8 DR1 I Data signal 9 DR0 I Data signal (LSB) 10 GND P Ground 11 DG7 I Data signal (MSB) 12 DG6 I Data signal 13 DG5 I Data signal 14 DG4 I Data signal 15 DG3 I Data signal 16 DG2 I Data signal 17 DG1 I Data signal 18 DG0 I Data signal (LSB) 19 GND P Ground 20 DB7 I Data signal (MSB) 21 DB6 I Data signal 22 DB5 I Data signal 23 DB4 I Data signal 24 DB3 I Data signal 25 DB2 I Data signal 26 DB1 I Data signal 27 DB0 I Data signal (LSB) 28 GND P Ground 29 SDA I Data input pin of SPl mode 30 CS I Chip select pin of SPI interface 31 SCL I Clock input pin of SPl mode 32 DCLK I Data-clock and oscillator source 33 Dummy1 Dummy Not connected 34 HSYNC I Horizontal synchronizing signal Remark Note1 Note1 Note1 Note1 Note1 Note1 Note1 Note1 Note2 Note2 Note2 Note2 Note2 Note2 Note2 Note2 Note3 Note3 Note3 Note3 Note3 Note3 Note3 Note3 35 VSYNC I Vertical synchronizin.