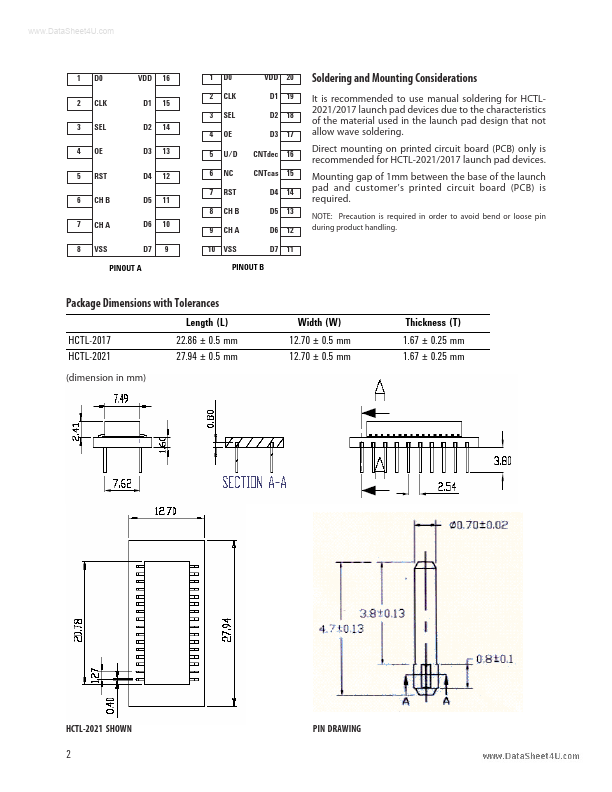

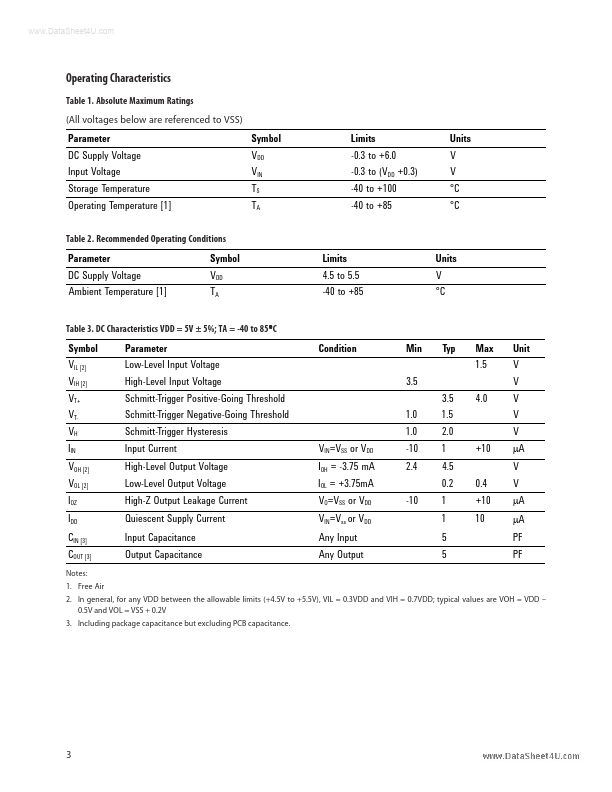

Datasheet Summary

..

HCTL-2017 and HCTL-2021

Quadrature Decoder/Counter Interface ICs

Data Sheet

Description

The HCTL-2021/2017 is CMOS ICs that performs the quadrature decoder, counter, and bus interface function. The HCTL-2021/2017 is designed to improve system performance in digital closed loop motion control systems and digital data input systems. It does this by shifting time intensive quadrature decoder functions to a cost effective hardware solution. The HCTL-2021/2017 consists of a quadrature decoder logic, a binary up/down state counter, and an 8-bit bus interface. The use of Schmitt-triggered CMOS inputs and input noise filters allows reliable operation in noisy environments....