APA150

APA150 is 2nd Generation Reprogrammable Flash Fpgas manufactured by Actel Corporation.

- Part of the APA600 comparator family.

- Part of the APA600 comparator family.

v3.0

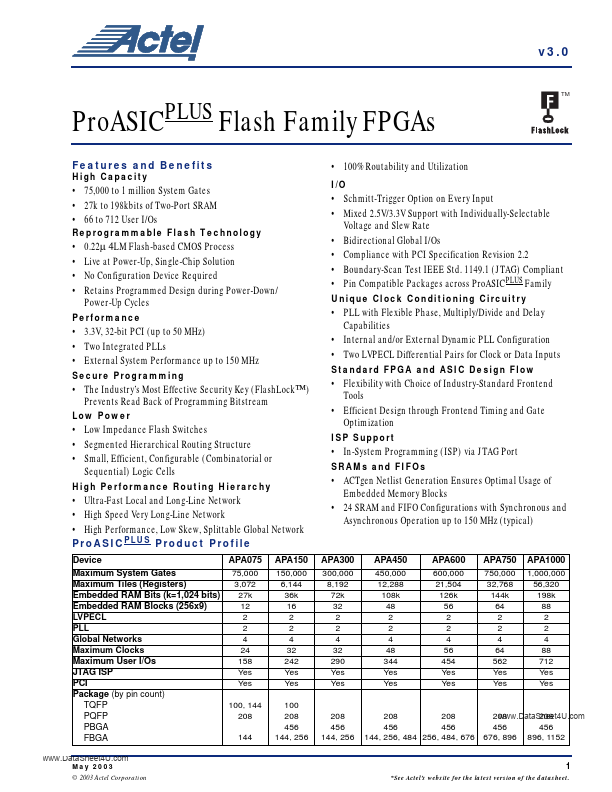

Pro ASICPLUS Flash Family FPGAs

Fe a t ur es an d B e ne f i ts

High C apaci t y

- 100% Routability and Utilization

I/O

- 75,000 to 1 million System Gates

- 27k to 198kbits of Two-Port SRAM

- 66 to 712 User I/Os

Rep ro gra m m able Fl as h T ech nol ogy

- -

- -

0.22µ 4LM Flash-based CMOS Process Live at Power-Up, Single-Chip Solution No Configuration Device Required Retains Programmed Design during Power-Down/ Power-Up Cycles

- Schmitt-Trigger Option on Every Input

- Mixed 2.5V/3.3V Support with Individually-Selectable Voltage and Slew Rate

- Bidirectional Global I/Os

- pliance with PCI Specification Revision 2.2

- Boundary-Scan Test IEEE Std. 1149.1 (JTAG) pliant

- Pin patible Packages across Pro ASICPLUS Family

Uni que Cl ock Con dit io ning C ir cui tr y

P erf orm a nce

- 3.3V, 32-bit PCI (up to 50 MHz)

- Two Integrated PLLs

- External System Performance up to 150 MHz

S ecur e Pr og ram m i ng

- PLL with Flexible Phase, Multiply/Divide and Delay Capabilities

- Internal and/or External Dynamic PLL Configuration

- Two LVPECL Differential Pairs for Clock or Data Inputs

S ta ndar d FP GA and AS IC De si gn F low

- The Industry’s Most Effective Security Key (Flash Lock) Prevents Read Back of Programming Bitstream

Low P ower

- Low Impedance Flash Switches

- Segmented Hierarchical Routing Structure

- Small, Efficient, Configurable (binatorial or Sequential) Logic Cells

Hig h P er f o r m ance R out ing H i era rc hy

- Flexibility with Choice of Industry-Standard Frontend Tools

- Efficient Design through Frontend Timing and Gate Optimization

IS P S uppo rt

- In-System Programming (ISP) via JTAG...