ARINC429

ARINC429 is Bus Interface manufactured by Actel.

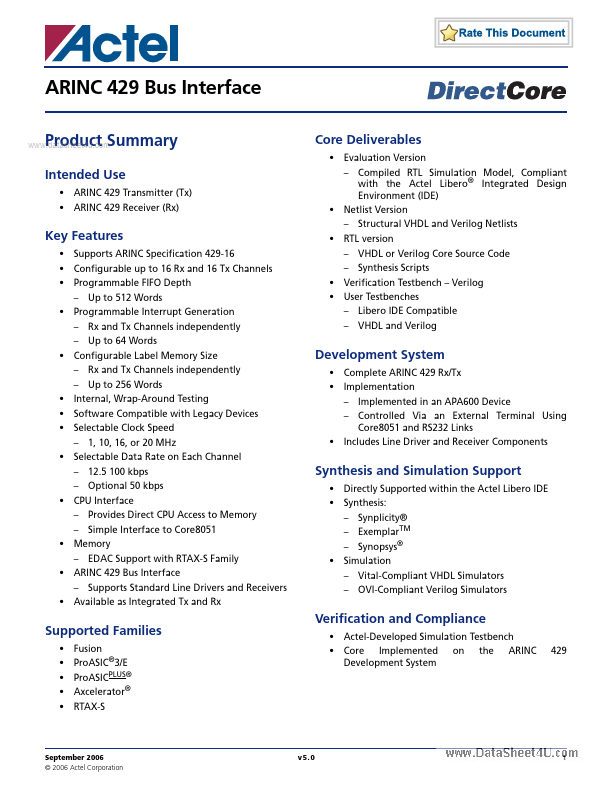

ARINC 429 Bus Interface

..

Product Summary

Intended Use

- - ARINC 429 Transmitter (Tx) ARINC 429 Receiver (Rx)

Core Deliverables

- Evaluation Version

- piled RTL Simulation Model, pliant with the Actel Libero® Integrated Design Environment (IDE) Structural VHDL and Verilog Netlists VHDL or Verilog Core Source Code Synthesis Scripts

- -

Netlist Version

- RTL version

- -

Key Features

- -

- - Supports ARINC Specification 429-16 Configurable up to 16 Rx and 16 Tx Channels Programmable FIFO Depth

- -

- -

- -

- -

- - Up to 512 Words Rx and Tx Channels independently Up to 64 Words Programmable Interrupt Generation

- -

Verification Testbench

- Verilog User Testbenches

-...