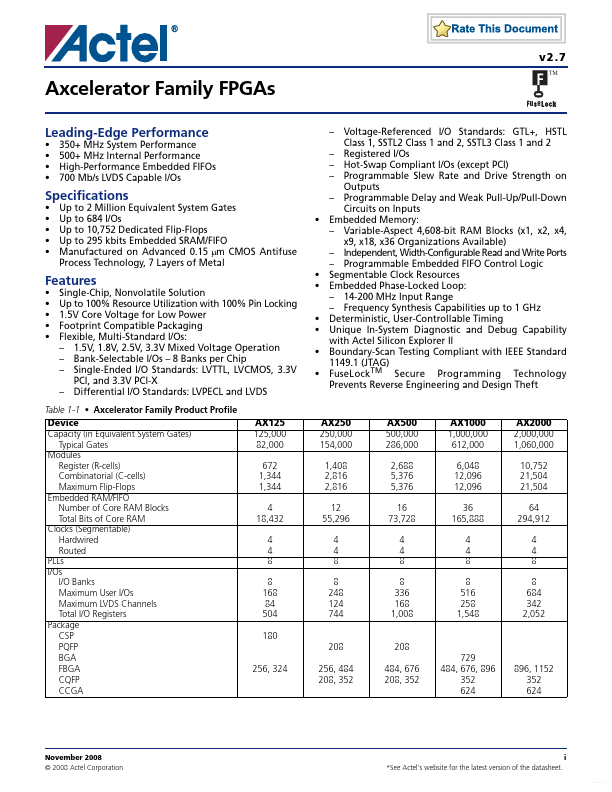

AX125

Key Features

- Voltage-Referenced I/O Standards: GTL+, HSTL Class 1, SSTL2 Class 1 and 2, SSTL3 Class 1 and 2 - Registered I/Os - Hot-Swap Compliant I/Os (except PCI) - Programmable Slew Rate and Drive Strength on Outputs - Programmable Delay and Weak Pull-Up/Pull-Down Circuits on Inputs Embedded Memory: - Variable-Aspect 4,608-bit RAM Blocks (x1, x2, x4, x9, x18, x36 Organizations Available) - Independent, Width-Configurable Read and Write Ports - Programmable Embedded FIFO Control Logic Segmentable Clock Resources Embedded Phase-Locked Loop: - 14-200 MHz Input Range - Frequency Synthesis Capabilities up to 1 GHz Deterministic, User-Controllable Timing Unique In-System Diagnostic and Debug Capability with Actel Silicon Explorer II Boundary-Scan Testing Compliant with IEEE Standard 1149.1 (JTAG) FuseLock TM Secure Programming Technology Prevents Reverse Engineering and Design Theft -