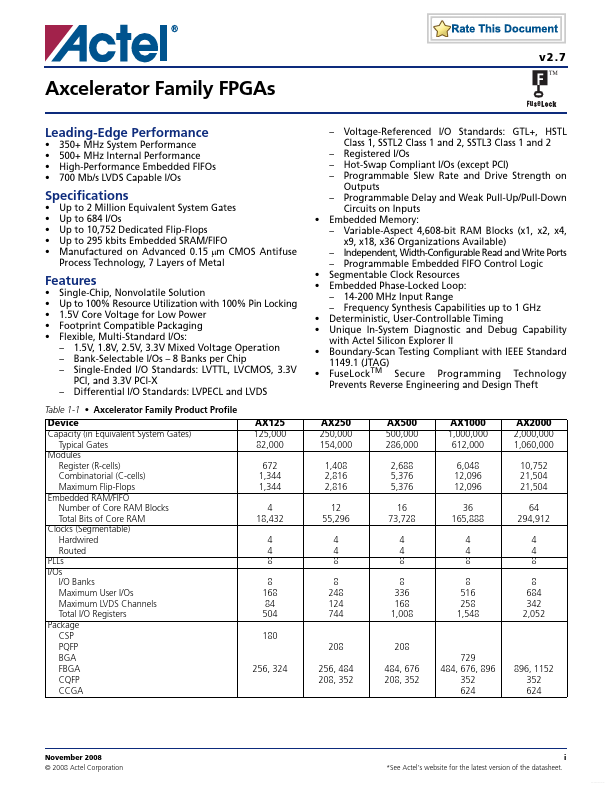

| Part | AX2000 |

|---|---|

| Description | Axcelerator Family FPGAs |

| Manufacturer | Actel |

| Size | 2.40 MB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| AX2011 | Philips Semiconductors | Portable CD Player |

| AX2003 | Philips Semiconductors | Portable CD Player |

| AX2000 | Philips Semiconductors | Portable CD Player |

| AX2002 | Philips Semiconductors | Portable CD Player |

| AX2001 | Philips Semiconductors | Portable CD Player |