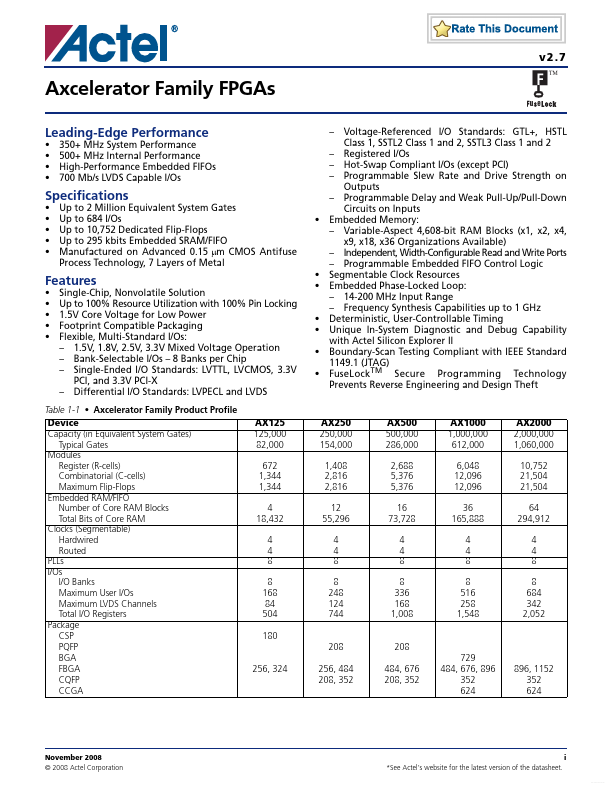

| Part | AX500 |

|---|---|

| Description | Axcelerator Family FPGAs |

| Manufacturer | Actel |

| Size | 2.40 MB |

Pricing from 2535.76 USD, available from NAC Semi and DigiKey.

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| NAC Semi | 46 | 60+ : 2535.76 USD | View Offer |

| DigiKey | 0 | 60+ : 2928.61833 USD | View Offer |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| AX500 | Roboteq | Dual Channel Digital Motor Controller |

| AX5043 | onsemi | Advanced High Performance ASK and FSK Narrow-band Transceiver |

| AX5031 | onsemi | Advanced multi-channel single chip UHF transmitter |

| AX5051 | onsemi | Advanced Multi-channel Single Chip UHF Transceiver |

| AX5051-510 | AXSEM | 470-510 MHz ASK/FSK/PSK Transceiver |