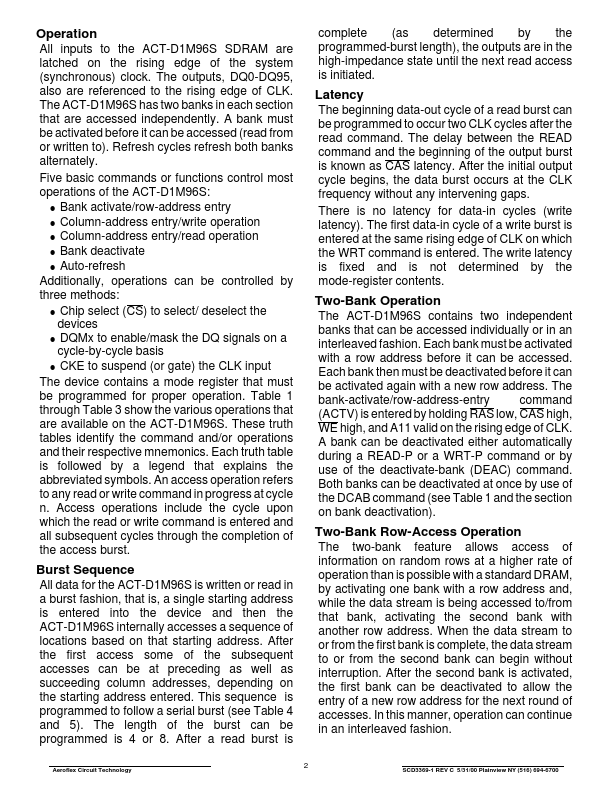

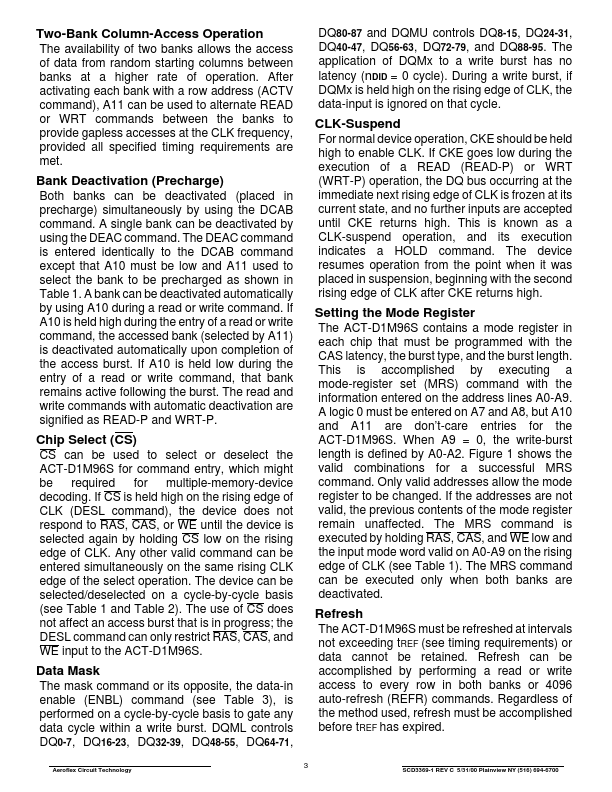

Datasheet Summary

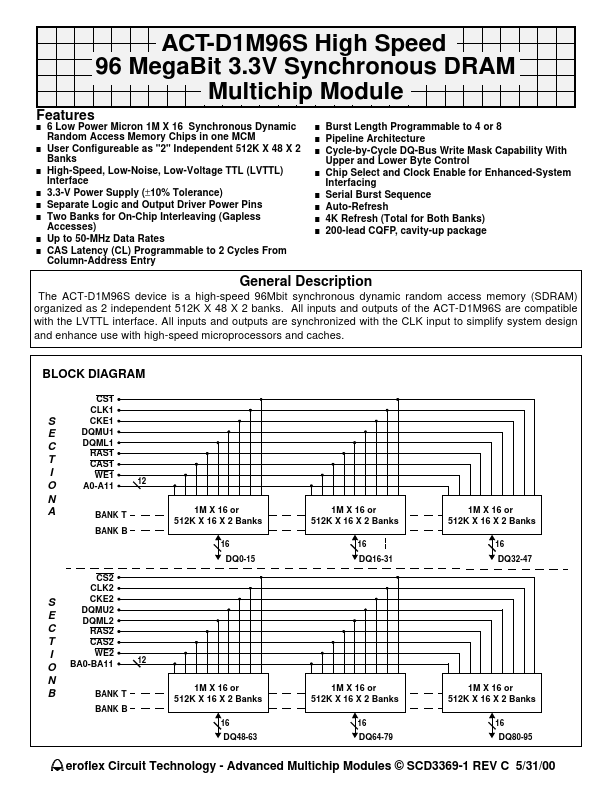

ACT-D1M96S High Speed 96 MegaBit 3.3V Synchronous DRAM Multichip Module

Features

6 Low Power Micron 1M X 16 Synchronous Dynamic Random Access Memory Chips in one MCM User Configureable as "2" Independent 512K X 48 X 2 Banks High-Speed, Low-Noise, Low-Voltage TTL (LVTTL) Interface 3.3-V Power Supply (±10% Tolerance) Separate Logic and Output Driver Power Pins Two Banks for On-Chip Interleaving (Gapless Accesses) Up to 50-MHz Data Rates CAS Latency (CL) Programmable to 2 Cycles From Column-Address Entry

Burst Length Programmable to 4 or 8 Pipeline Architecture Cycle-by-Cycle DQ-Bus Write Mask Capability With Upper and Lower Byte Control Chip Select and...