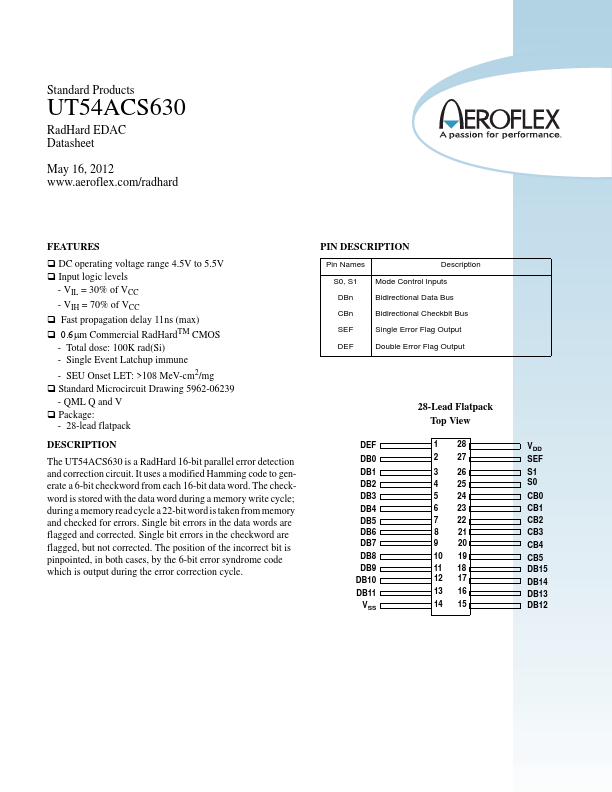

Datasheet Summary

Standard Products

RadHard EDAC Datasheet

May 16, 2012 .aeroflex./radhard

Features

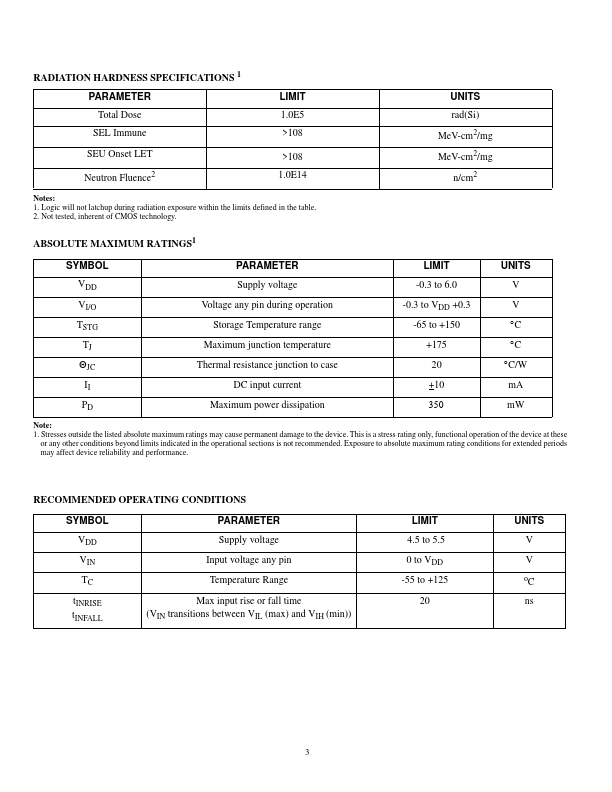

DC operating voltage range 4.5V to 5.5V Input logic levels

- VIL = 30% of VCC

- VIH = 70% of VCC Fast propagation delay 11ns (max) m mercial RadHardTM CMOS

- Total dose: 100K rad(Si)

- Single Event Latchup immune

- SEU Onset LET: >108 MeV-cm2/mg Standard Microcircuit Drawing 5962-06239

- QML Q and V Package:

- 28-lead flatpack

DESCRIPTION

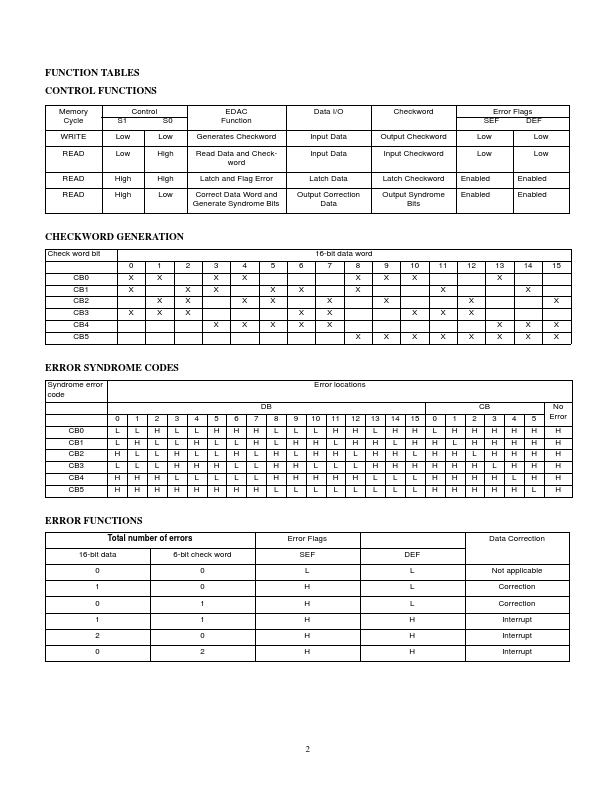

The UT54ACS630 is a RadHard 16-bit parallel error detection and correction circuit. It uses a modified Hamming code to generate a 6-bit checkword from each 16-bit data word. The checkword is stored with the data word during a memory write...