LCK4801 Overview

Description

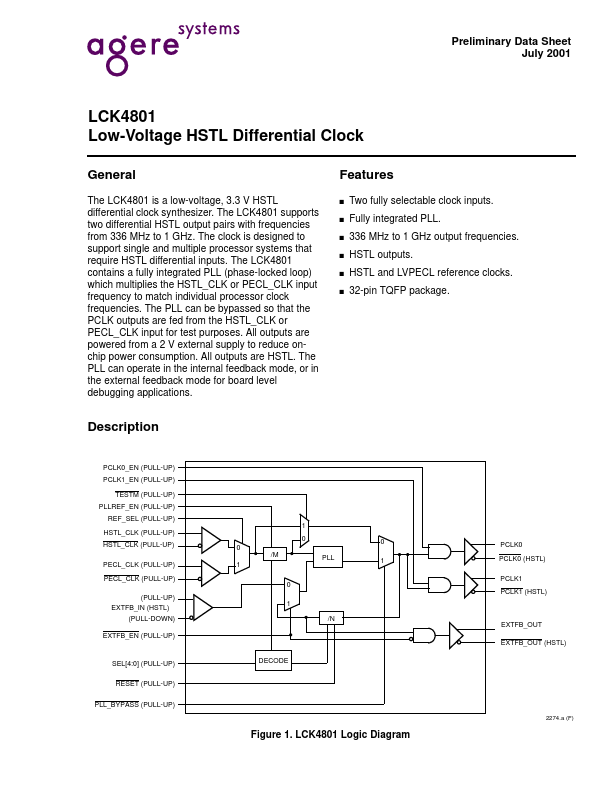

PCLK0_EN (PULL-UP) PCLK1_EN (PULL-UP) TESTM (PULL-UP) PLLREF_EN (PULL-UP) REF_SEL (PULL-UP) 1 HSTL_CLK (PULL-UP) HSTL_CLK (PULL-UP) PECL_CLK (PULL-UP) PECL_CLK (PULL-UP) (PULL-UP) EXTFB_IN (HSTL) (PULL-DOWN) EXTFB_EN (PULL-UP) EXTFB_OUT (HSTL) SEL[4:0] (PULL-UP) RESET (PULL-UP) PLL_BYPASS (PULL-UP) 2274.a (F) 0 0 /M 1 0 1 /N PLL 0 1 PCLK0 PCLK0 (HSTL) PCLK1 PCLK1 (HSTL) EXTFB_OUT DECODE Figure 1. LCK4801 Logic Diagram LCK4801 Low-Voltage HSTL Differential Clock Preliminary Data Sheet July 2001 Description (continued) PLL_BYPASS PLLREF_EN VDDHSTL VSS RESET SEL[4] SEL[3] SEL[2] SEL[1] SEL[0] VDDA 24 25 26 27 28 29 30 31 32 1 VDDD 23 22 21 20 19 18 17 16 15 14 13 12 11 10 VDDHSTL PCLK0 PCLK0 PCLK1 PCLK1 EXTFB_OUT EXTFB_OUT VDDHSTL EXTFB_IN EXTFB_IN EXTFB_EN PECL_CLK PECL_CLK 2 TESTM 3 VSS 4 PCLK0_EN 5 PCLK1_EN 6 REF_SEL 7 HSTL_CLK 8 HSTL_CLK 9 2275 (F) Figure 2.

Key Features

- s s s s s s Two fully selectable clock inputs

- Fully integrated PLL

- 336 MHz to 1 GHz output frequencies

- HSTL and LVPECL reference clocks

- 32-pin TQFP package