OR2T08A

Key Features

- IEEE is a registered trademark of The Institute of Electrical and Electronics Engineers, Inc. Table

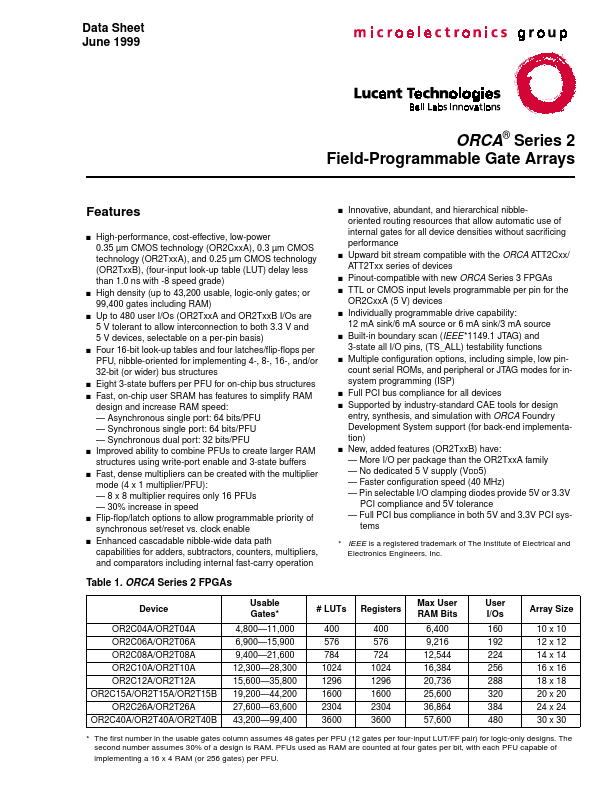

- ORCA Series 2 FPGAs Device OR2C04A/OR2T04A OR2C06A/OR2T06A OR2C08A/OR2T08A OR2C10A/OR2T10A OR2C12A/OR2T12A OR2C15A/OR2T15A/OR2T15B OR2C26A/OR2T26A OR2C40A/OR2T40A/OR2T40B Usable Gates* 4,800-11,000 6,900-15,900 9,400-21,600 12,300-28,300 15,600-35,800 19,200-44,200 27,600-63,600 43,200-99,400 # LUTs 400 576 784 1024 1296 1600 2304 3600 Registers 400 576 724 1024 1296 1600 2304 3600 Max User RAM Bits 6,400 9,216 12,544 16,384 20,736 25,600 36,864 57,600 User I/Os 160 192 224 256 288 320 384 480 Array Size 10 x 10 12 x 12 14 x 14 16 x 16 18 x 18 20 x 20 24 x 24 30 x 30

- The first number in the usable gates column assumes 48 gates per PFU (12 gates per four-input LUT/FF pair) for logic-only designs. The second number assumes 30% of a design is RAM. PFUs used as RAM are counted at four gates per bit, with each PFU capable of implementing a 16 x 4 RAM (or 256 gates) per PFU. ORCA Series 2 FPGAs Data Sheet June 1999 Table of Contents Contents Page Contents Page