ARG81300

ARG81300 is Single LNB Supply and Control Voltage Regulator manufactured by Allegro MicroSystems.

FEATURES

AND BENEFITS

- Integrated boost MOSFET, current sensing, and pensation

- Stable with low-profile ceramic boost capacitors

- 704 k Hz switching frequency for small low-cost ponents

- S¯¯L¯¯E¯¯E¯¯P pin for ultralow power consumption mode

- Adjustable LNB output current limit (250 to 950 m A- ) with shutdown timer

- Covers wide array of application requirements

- Minimizes ponent sizing to fit each application

- For startup, reconfiguration, and continuous output

- Boost peak current limit scales with LNB current limit

Continued on the next page…

PACKAGE:

16-contact QFN (suffix ES) 3 mm × 3 mm × 0.75 mm

DESCRIPTION

The ARG81300 is a single-channel low-noise block regulator (LNBR). The ARG81300 consists of a monolithic boost converter followed by a low-drop linear regulator. It is specifically designed to provide the power and the interface signals to an LNB down converter via coaxial cable in satellite TV receiver systems.

The ARG81300 requires few external ponents, with the boost switch and pensation circuitry integrated inside of the device. The 704 k Hz switching frequency and user-controlled output current limit minimize the size of the passive filtering ponents.

The I2C™-patible interface provides control capabilities for plex system requirements, as well as diagnostic capabilities for system fault reporting.

A sleep pin is available to maximize power savings and to quickly shut down the device if needed, without using I2C™ control.

The ARG81300 is provided in a small 3 × 3 mm QFN package with exposed pad for thermal dissipation. It is lead (Pb) free, with 100% matte-tin leadframe plating.

Not to scale

C2 2 × 4.7 µF or 1 × 10 µF

C1 100 n F

VIN VREG

C3 220 n F

GND PAD

VDD R1 R2 R3 R4 R5 C7

100 n F

TCAP

TONECTRL SDA

SCL ADD

SLEEP

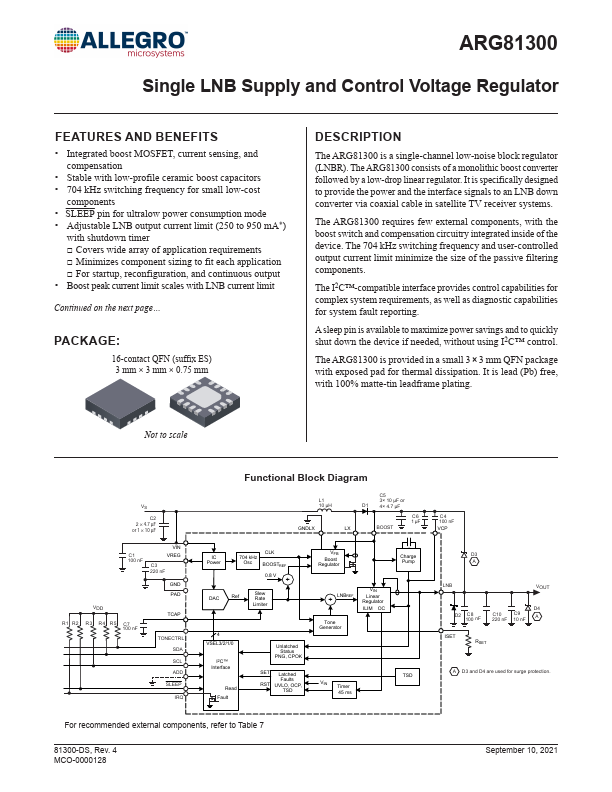

Functional Block Diagram

L1 10 µH GNDLX

C5 3× 10 µF or D1 4× 4.7 µF

C6 1...