AS9C25256M2018L

AS9C25256M2018L is 2.5V 512/256K x 18 Synchronous Dual-port SRAM manufactured by Alliance Semiconductor Corporation.

Features

- True Dual-Port memory cells that allow simultaneous access of the same memory location

- Organisation: 524,288/262,144 × 18[1]

- Fully Synchronous, independent operation on both ports

- Selectable Pipeline or Flow-Through output mode

- Fast clock speeds in Pipeline output mode: 250 MHz operation (9Gbps bandwidth)

- Fast clock to data access: 2.8ns for Pipeline output mode

- Asynchronous output enable control

- Fast OE access times: 2.8ns

- Double Cycle Deselect (DCD) for Pipeline Output Mode

- 19/18[1]-bit counter with Increment, Hold and Repeat features on each port

Note: 1. AS9C25512M2018L/AS9C25256M2018L

- -

- -

- -

- -

Dual Chip enables on both ports for easy depth expansion Interrupt and Collision Detection Features

2.5 V power supply for the core LVTTL patible, selectable 3.3V or 2.5V power supply for I/Os, addresses, clock and control signals on each port Snooze modes for each port for standby operation 15m A typical standby current in power down mode Available in 256-pin Ball Grid Array (BGA), 144-pin Thin Quad Flatpack (TQFP) and 208-pin fine pitch Ball Grid Array (fp BGA) Supports JTAG features pliant with IEEE 1149.1

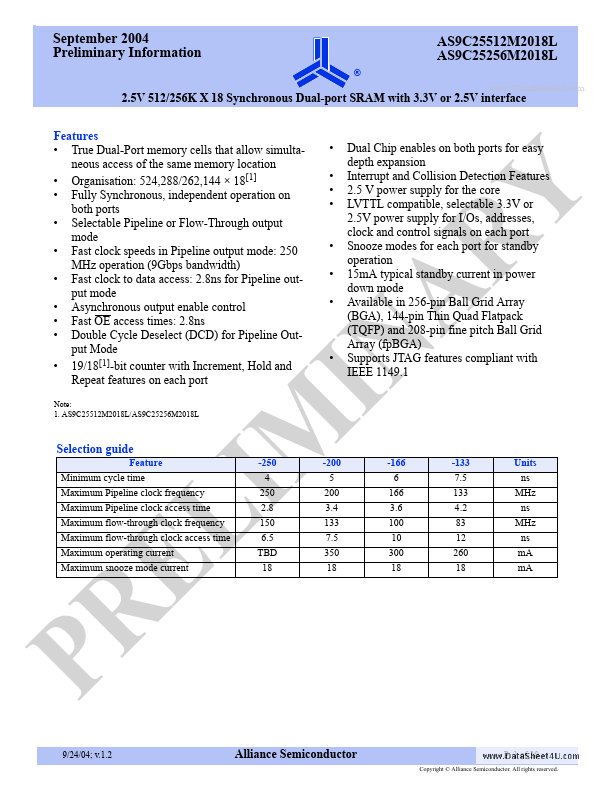

Selection guide

Feature

Minimum cycle time Maximum Pipeline clock frequency Maximum Pipeline clock access time Maximum flow-through clock frequency Maximum flow-through clock access time Maximum operating current Maximum snooze mode current -250 4 250 2.8 150 6.5 TBD 18 -200 5 200 3.4 133 7.5 350 18 -166 6 166 3.6 100 10 300 18 -133 7.5 133 4.2 83 12 260 18 Units ns MHz ns MHz ns m A m A

9/24/04; v.1.2

Alliance Semiconductor

P. 1 of 30

Copyright © Alliance Semiconductor. All rights reserved.

AS9C25512M2018L AS9C25256M2018L

®

..

Dual port logic block diagram

R/W Control

R/W Control

BE1A-BE0A CE0A CE1A R/WA

REGISTER BANK

REGISTER BANK

REGISTER BANK

REGISTER...