AS7C513B Description

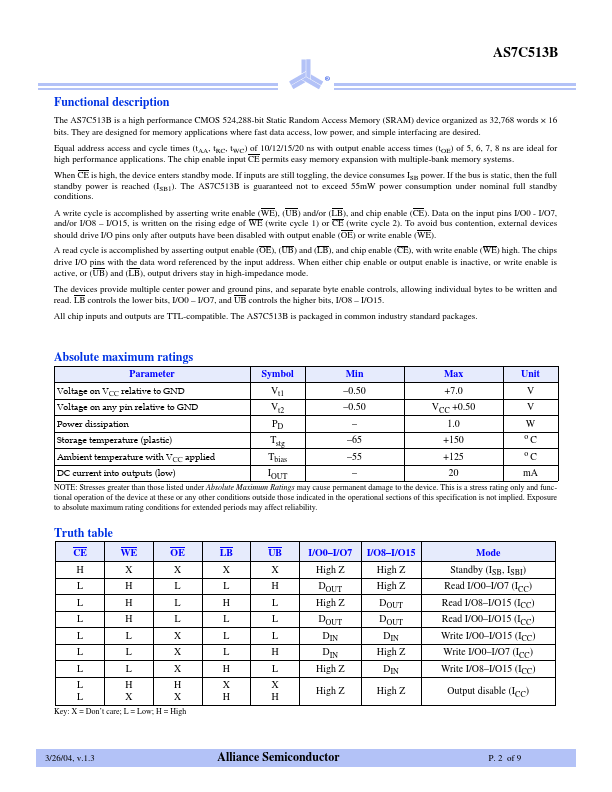

The AS7C513B is a high performance CMOS 524,288-bit Static Random Access Memory (SRAM) device organized as 32,768 words × 16 bits. They are designed for memory applications where fast data access, low power, and simple interfacing are desired. Equal address access and cycle times (tAA, tRC, tWC) of 10/12/15/20 ns with output enable access times (tOE) of 5, 6, 7, 8 ns are ideal for high performance applications.

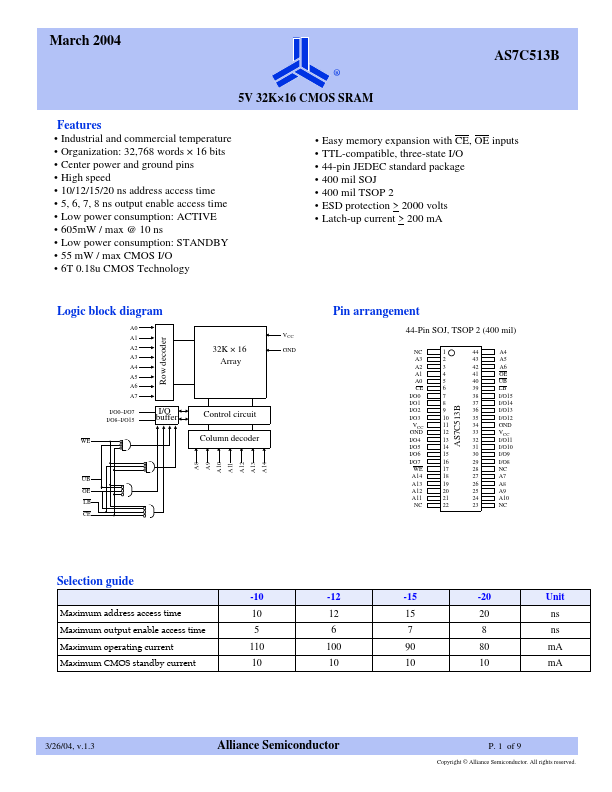

AS7C513B Key Features

- Industrial and mercial temperature

- Organization: 32,768 words × 16 bits

- Center power and ground pins

- High speed

- 10/12/15/20 ns address access time

- 5, 6, 7, 8 ns output enable access time

- Low power consumption: ACTIVE

- 605mW / max @ 10 ns

- Low power consumption: STANDBY

- 55 mW / max CMOS I/O