D1s Overview

Key Specifications

Max Operating Temp: 70 °C

Min Operating Temp: -25 °C

Description

Confidential Revision History Copyright© Allwinner Technology Co.,Ltd.

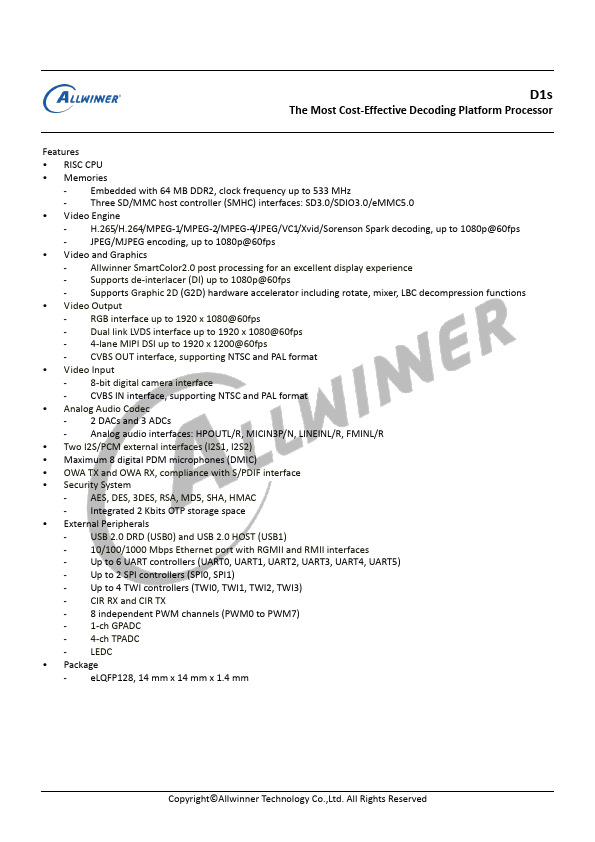

Key Features

- Embedded with 64 MB DDR2, clock frequency up to 533 MHz

- Three SD/MMC host controller (SMHC) interfaces: SD3.0/SDIO3.0/eMMC5.0 Video Engine

- JPEG/MJPEG encoding, up to 1080p@60fps Video and Graphics

- Allwinner SmartColor2.0 post processing for an excellent display experience

- Supports de-interlacer (DI) up to 1080p@60fps